# Are 2 beller Chan 1?

(Lee Ritchey Says No!)

Embedding Magnetics Understanding BGA Anomalies Low-Temperature Soldering This issue of Printed Circuit Design & FAB/Circuits Assembly is brought to you by:

PCB WEST 2020 Conference & Exhibition V I R T U A L

Exhibition: September 9 – 10 Conference: September 7 – 10

### PCBWEST.COM

### **CONNECTING DESIGN TO FAB TO ASSEMBLY**

Visit the virtual exhibition Download valuable content 125+ hours of on-demand tech talks O

All-inclusive conference pass for \$895 through August 12th

###

# GET OUR NEW IPC CLASS 3 DESIGN GUIDE!

The must-knows and guidelines for your aerospace, military and other high-reliability boards.

### DOWNLOAD NOW

https://pages.protoexpress.com/ipc-class-3-design-guide.html

RUSHPCB

20 YEARS OF MANUFACTURING EXPERIENCE WITH BLIND AND BURIED VIAS, RIGID FLEX & FLEX PCB ELECTRONIC DESIGN, & QUICK TURN CIRCUIT BOARDS, ASSEMBLY & FULL TURNKEY

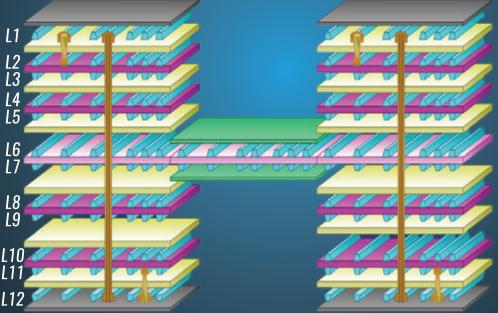

## **Multilayer PCB Stackup**

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

### When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

### Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

**Certified: ISO9001/ITAR/UL** www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O' Toole Ave, San Jose, CA 95131, U.S.A

#### FIRST PERSON

#### 6 CAVEAT LECTOR

The virtues of virtual. Mike Buetow

#### MONEY MATTERS

#### 14 ROI

To remain flexible, we need to stay fit. **Peter Bigelow**

#### 15 FOCUS ON BUSINESS

With travel frozen, rethink and repurpose those marketing dollars. Susan Mucha

#### TECH TALK

17 **DESIGNER'S NOTEBOOK** Studying the library.

John Burkhert

#### 19 MATERIAL GAINS

High reliability starts at the lowest level. Alun Morgan

#### 20 THE FLEXPERTS

Navigating the flex roadmap. Mark Finstad

#### 42 SCREEN PRINTING

Embrace the remote. Clive Ashmore

43 TECH TIPS Low-temperature soldering heats up. Timothy O'Neill

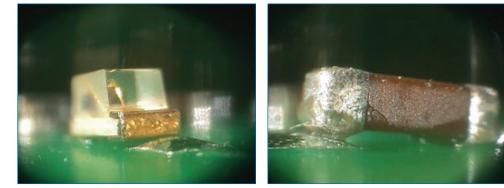

#### 44 DEFECT OF THE MONTH Lifted parts. Bob Willis

48 TECHNICAL ABSTRACTS

#### DEPARTMENTS

- 8 AROUND THE WORLD

- 13 MARKET WATCH

- 45 OFF THE SHELF

- 47 MARKETPLACE

### PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

#### **FEATURES**

#### 22 ROUTING *cover story*

#### Why Not Route Two Traces Between Pins on a 1mm Pitch BGA?

Application notes describe how to save layers in a PCB by routing two traces between pins on a 1mm pitch BGA. Are they correct? by LEE RITCHEY

Dy LEE KITCHET

#### 29 **RF DESIGN**

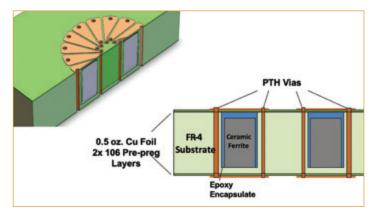

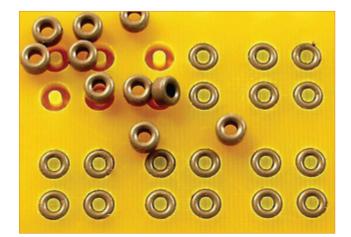

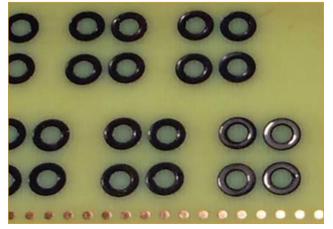

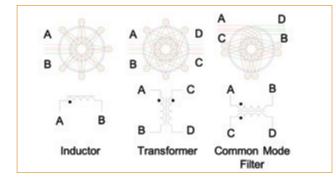

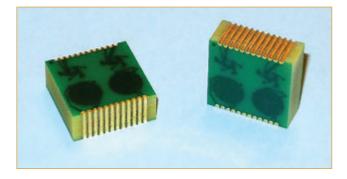

#### Embedding Magnetics in a PCB Design

Transformers and inductors used in power and telecommunication applications are often the more

expensive devices in a system design. When realizing a power converter or RF module, cost and size reductions can be realized by combining the magnetics and PCB functions. by JIM QUILICI

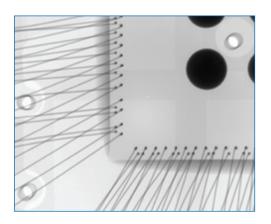

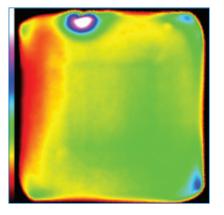

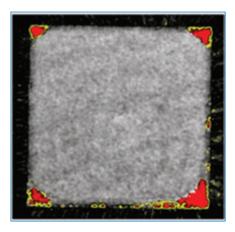

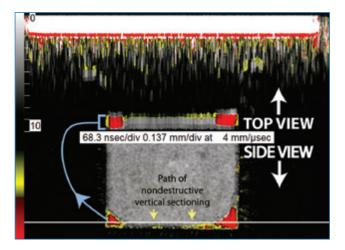

#### 31 COMPONENT INSPECTION

#### Hidden Trouble in a BGA Package

Does a small node suggest anomalies – and potential failure? A combined x-ray and ultrasound process investigates. by TOM ADAMS

#### 34 OPERATIONS

#### Leveraging Systems and Processes to Evolve NPI

Covid-19 drove a new medical device OEM to request a product ramp at high speed when other supply chain options were unexpectedly shut down. How a cross-functional team model and real-time systems completed an 800-piece validation order in fewer than 10 days and began full production in less than two weeks. by JOHN SAMMUT

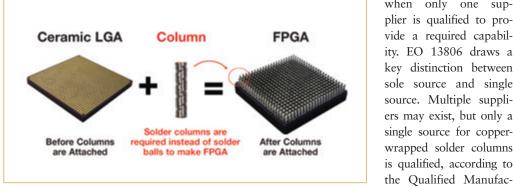

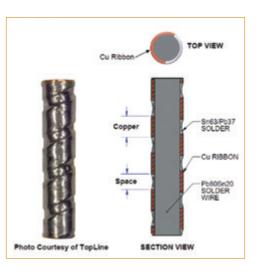

#### 37 COMPONENTS

#### FPGA Issues and Concerns: A Real Danger and a Call to Action

Five recommendations for ensuring long-term access to key component packages. by MARTIN HART

#### IN THE DIGITAL EDITION

#### The Digital Route The grand opening of the Printed Circuit Engineers Association. by KELLY DACK

#### ON PCB CHAT (pcbchat.com)

Benchmark Lark's New Fab/Assembly/Test Plant with KEVIN WALKER

Electronic Debugging Tools with INSPECTAR

Supply Chain Changes in the Covid Era with CHRISTOPHER TANG, PH.D.

# The All New EDA Store

#### Zero Impedance CAD Purchasing.

Visit the all-new EMA online storefront and shop our collection of CAD products anytime; day or night. Here you will find a broad array of products to help you design faster and more efficiently. Should you need it, our team of experts are here to help answer questions, provide demos, and support you through CAD tool selection.

Best of all, you can rest easy with our upfront, transparent, and hassle-free purchasing process.

#### Visit the EMA Store at go.ema-eda.com/eda-store >

#### COMPREHENSIVE PCB DOCUMENTATION

#### Use 3D Models for Superior PCB Assembly Illustrations

Manage Layer Stackup Design and Materials

Visit us at **PCB West Virtual** September 9 - 10

### BluePrint PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings to drive fabrication.

of imported CAD data as a 3D PCB

Lowers documentation cost and time

Increases documentation detail & accuracy

Shortens PCB design cycles

Reduces documentation time by 60-80%

#### downstreamtech.com • (508) 970-0670

©2020 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

### PRINTED CIRCL **DESIGN**& FA pcdandf.com

circuitsassembly.com

#### **EDITORIAL**

EDITOR IN CHIEF Mike Buetow 617-327-4702 | mbuetow@upmediagroup.com

SENIOR EDITOR Chelsey Drysdale 949-295-3109 | cdrysdale@upmediagroup.com

DESIGN TECHNICAL EDITOR Pete Waddell

EDITORIAL OFFICE P.O. Box 470, Canton, GA 30169 | 888-248-7020

#### PCD&F CONTRIBUTING EDITORS

Akber Roy, Peter Bigelow, John Burkhert, Mark Finstad, Bryan Germann, Bill Hargin, Nick Koop, Greg Papandrew

CIRCUITS ASSEMBLY CONTRIBUTING EDITORS AND ADVISORS Clive Ashmore, David Bernard, Robert Boguski, John D. Borneman, Joseph Fama, Susan Mucha, Chrys Shea, Jan Vardaman, Ranko Vujosevic

#### PRODUCTION

ART DIRECTOR AND PRODUCTION blueprint4MARKETING, Inc. | production@upmediagroup.com

#### **SALES**

SALES DIRECTOR Frances Stewart 678-817-1286 | fstewart@upmediagroup.com

SENIOR SALES ASSOCIATE Brooke Anglin 404-316-9018 | banglin@upmediagroup.com EXHIBIT SALES

Frances Stewart 678-817-1286 | fstewart@upmediagroup.com PRINT/FLECTRONIC REPRINTS

cdrysdale@upmediagroup.com

#### SUBSCRIPTIONS

For changes, additions or cancelations: subscriptions@upmediagroup.com

#### **UP MEDIA GROUP, INC.**

PRESIDENT Pete Waddell

VICE PRESIDENT. SALES AND MARKETING Frances Stewart

VICE PRESIDENT. EDITORIAL AND PRODUCTION Mike Buetov

DIRECTOR OF GROUP SHOWS

Alyson Corey acorey@upmediagroup.com

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. For others, annual Subscription Rates in U.S. funds are: \$80 (U.S. and Canada), \$145 (all other countries). Single copy price is \$8.50. All subscription and single copy orders or inquiries should be directed to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169, email subscriptions@upmediagroup.com. Photocopies and issues on Microfilm/Microfiche (16mm, 33mm or 105mm) are available from University Microfilms International, 300 N. Zeeb Rd., Ann Arbor, MI 48106, Telephone 313-761-4600.

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by UP Media Group Inc., PO Box 470 Canton, GA 30169. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

Periodicals postage paid at Canton/Ball Ground, GA, and additional mailing offices. © 2020, UP Media Group, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS Assembly is forbidden without written permission.

Postmaster: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169.

# Thin Lamination Board

TLB, a global leader in the 4th industrial revolution.

### **TRUST 2030**

Good Company in 20 Years, Great Company in 30 Years.

**TLB** is specialized in manufacturing PCB for semiconductors. By joining World Class 300 in 2018, we have become a company specializing in materials and components leading the fourth industrial revolution. Based on technology and quality, we will establish ourselves as a material parts company that leads not only Korea PCB but also world PCB.

#### DRAM Module / SSD Module

#### IOT / Build-up Board

#### Semiconductor TEST B'd & 5G Network System

#### TLB CO., LTD.

**15602) 305, Sinwon-ro, Danwon-gu, Ansan-si, Gyeonggi-do 16BL 17LT Tel.** 031-8040-2096 Fax. 031-492-6623 Domestic Tel. 031-8040-2071, E-Mail. cmh@tlbpcb.com Offshore Tel. 031-8040-2060, E-Mail. will\_shin@tlbpcb.com

#### CAVEAT LECTOR

MIKE BUETOW EDITOR-IN-CHIEF

### Living in the Virtual World

**S** OME 13 YEARS ago, UP Media Group launched the first virtual trade show for the electronics industry. In some ways – most, probably – we were ahead of the times. People liked it because it was simple to attend, but the platform wasn't ready for prime time.

That's not to say it was technically subpar. You could pop in and out of booths and talk to the personnel waiting for you, and I still feel for those folks who, driven by caffeine and excitement (or just an affinity for self-abuse), kept vigil around the clock as attendees in different time zones came on line and into the show. And we held webinars and chats with high-profile experts like Dr. Eric Bogatin. But in the end, attendees seemed to prefer meeting with peers face to face.

Covid-19 is injecting itself into almost every facet of our work and home lives, however, and we have to make some concessions to the times. As such, we have made the difficult but necessary decision to make PCB West a virtual event this year. The call was made following a survey of past attendees and talks with our more than 100 exhibitors.

We are pleased to announce, however, that almost all the technical sessions originally slated for the live PCB West will now be available on demand, starting Sept. 7. That's more than 125 hours' worth of high-end technical training. For the full list, see the conference catalog at pcbwest.com.

On the plus side, even those with severe travel restrictions will be able to participate in this year's show. Each year, we receive feedback from conferencegoers that there's more presentations to hear than they can get to in four days. Since PCB West Virtual 2020 is all on-demand, attendees won't have to pick and choose this year. Some of the speakers will be available for live question/answer sessions following their presentations. And like the physical show, attendees will receive certificates indicating the number of hours of training received at PCB West.

The exhibitors will be there of course, too. We are grateful to the many companies using this event as a chance to reach new customers. We also welcome the Printed Circuit Engineering Association, the trade group launched earlier this year (and in the interest of disclosure, I'm a director), which will be on hand to talk about its plans for promoting the printed circuit engineering profession.

While I'm on the subject, two of the contributors to this month's issue are also speaking at PCB West Virtual 2020. Mark Finstad will join co-Flexperts columnist Nick Koop in covering the gamut of flexible and rigid-flex circuits, from material selection and cost drivers to design tips for better physical and electrical performance. And Lee Ritchey will give a pair of fiveplus-hour tutorials on power delivery system design and stackup design.

I firmly believe that when the threat of Covid-19 has been mitigated, we will go back to populating offices and factories, and will do so gladly. Same goes for making sales calls and plant visits, and yes, going to industry events like conferences and trade shows. It may not occur immediately, but over time it will happen.

We aren't there yet, unfortunately, at least not in the United States. Yet training and education must go on. Companies must get to know potential vendors, and designers and engineers must continue to expand their networks. Trade shows remain a highly effective way to do that.

So, with apologies for the promotion, I hope readers from around the world take advantage of this oneof-a-kind opportunity to hear and learn from the best our industry has to offer at PCB West Virtual 2020 in September.

mbuetow@upmediagroup.com @mikebuetow

6 PRINTED CIRCUIT DESIGN & FAB / CIRCUITS ASSEMBLY

### Where Advanced Technology, **Highest Quality & Fastest Delivery Are Standard**

APCT Offers Printed Circuit Board Solutions from NPI to Mass Production

- Standard to Advanced HDI Technology

- Flex and Rigid Flex Technology

- Complete DFM Support

- Cycle Times Faster Than Industry Standards

- Defense & Aerospace Certifications

- Global Offshore Solutions

- Advantages Include:

- Ease of Use

- Seamless Recipe Transfer

- Inventory Management

- Risk Mitigation

#### Contact APCT Today 408.727.6442 | APCT.com

#### Circuit Board Solutions Printed

APCT.com

APCT Santa Clara HQ 408,727,6442

714.921.0860

714.993.0270

APCT Anaheim APCT Orange County APCT Wallingford 203.269.3311

APCT Global 203.284.1215

#### **PCDF** People

Bowman promoted **Jeffrey Korpus** to manager of the company's Standards business Unit. He formerly was project manager and support engineer with responsibility for new

standards design and team management, and managed Bowman's quality system.

**Charles Pfeil** has released the second version of his e-book on *High-Speed Constraint Values and PCB Layout Methods,* available at pcdandf.com.

MacDermid Alpha appointed Fabio Taiana vice president Assembly Solutions – Europe.

Sierra Circuits named **Roy Alcus** director of manufacturing.

#### **PCDF Briefs**

The Air Force Research Laboratory will allocate \$154 million to NextFlex to fund flexible hybrid electronics research for 3-D printing.

**Bold Laser Automation** shipped a LPW2424 laser precision welding system.

Dongguan Tanjin Electronic Technology will invest \$28 million to build an Al-based Cu-clad foil production project in the Chongqing Western Electronic Circuit Industrial Park in China. Annual output value is expected to reach \$85 million.

Huangshi Guanghe Circuit has begun construction on a new PCB fabrication plant in Hubei Province.

**IPC** membership has voted to accept a new addition covering medical devices to the industry standard for bare board qualification and acceptability following industry review. IPC-6012 Medical Device Addendum should be ready by the end of this summer, says the task group chairman, Jan Pedersen of **Elmatica**.

**IPC** and the **HDP Users Group** signed a memorandum of understanding enabling a partnership, increased technical collaboration between groups, and a mutual path toward emerging and disruptive high-density interconnect technologies.

**Isola** has officially opened an expanded R&D and analytical services laboratory at the company's new global headquarters in Chandler, AZ.

**Matrix USA** received a trademark registration for its Europads PCB lamination press pads.

**MFS Technology** has completed the first phase of a major expansion of its flex circuit plant in Yiyang, Hunan, and will launch volume production this month.

Rogers named Krayden distributer in the US.

#### UPMG Announces Technical Sessions for PCB West Virtual 2020

**ATLANTA** – UP Media Group announced more than 40 technical sessions – totaling more than 125 hours – have been selected for PCB West Virtual 2020 this fall. The conference, which is moving to an online platform because of the novel coronavirus, takes place Sept. 7-10.

This year's conference features a pair of extended talks from Lee Ritchey on power delivery system design and stackup design, two talks from Dr. Eric Bogatin, and three full days of classes from Rick Hartley. The conference covers everything from RF/microwave and mixed-signal design, circuit grounding, understanding material choices, flex circuits, signal and power integrity, to fabrication and assembly processes. Talks are aimed at the spectrum of backgrounds, from novice to advanced.

"Like most conferences, we are putting the safety of our speakers and registrants ahead of any other priority. That said, we are elated to bring the best of the industry together for this unique technical conference," said Mike Buetow, PCB West conference director and editorial director, UPMG. "Even those with severe travel restrictions will be able to participate in this year's show. We will have more than 125 hours of training available – and the best part is, since it's all on-demand, attendees won't have to pick and choose which presentations to see."

"As an added bonus, some of the speakers will be available for live question/ answer sessions following their presentations," Buetow added.

New presentations will be made available throughout the week and will be available on-demand for 30 days. Attendees will receive certificates indicating the number of hours of training received at PCB West.

PCB West annually provides a conference and exhibition focused on the design and manufacture of PCBs, HDI, electronics assembly and circuit board test. For more information about PCB West, visit pcbwest.com. (MB)

### IPC, IAEG Encourage Use of IPC-1754 in Aerospace, Defense Industry

**BANNOCKBURN, IL** – IPC and International Aerospace Environmental Group issued a joint statement encouraging use of IPC-1754, *Materials and Substances Declaration for Aerospace and Defense and Other Industries*, in the aerospace and defense industry and its global supply chain.

Obtaining data from the supply chain to support chemical content reporting for article (hardware) products remains challenging and resource-intensive for industries such as aerospace and defense, the trade groups said. Increasing use of materials and substances declaration standards promotes efficiency in obtaining such data, however.

The standard, which is voluntary, supports data acquisition for various substance reporting requirements for article products, including data required by the EU's Waste Framework Directive for reporting to the SCIP database. Under the WFD, European article suppliers subject to SVHC reporting under REACH Article 33 will also be required to report SVHC data to the SCIP database. However, SCIP reporting will also require additional data elements such as material and product identifiers.

IPC-1754 supports all data elements needed for reporting to SCIP. In support of SCIP reporting, IPC is developing guidance for using IPC declaration standards when acquiring the necessary data. IAEG is also developing supporting general information for the use of IPC-1754 and related IAEG-developed tools in the AD industry supply chain, available on the IAEG website. (CD)

### SEMI AMERICAS EVENTS MARK YOUR CALENDAR!

JULY 20-22, 2020

The **Technology Leadership Series of the Americas** is a collection of seven major events representing the various technology communities in our industry. These programs connect the 2,300+ member companies and over 1.3 million

global professionals to advance the technology and business of electronics manufacturing and the design-supply chain.

There are numerous ways for you to participate in these events to connect with the industry and grow your business.

#### SAVE THE DATES FOR THESE 2020-2021 EVENTS

Explore these upcoming programs and fill out the Interest Form on each website to get connected for the latest event updates.

**Panasonic** will ramp up its production of 5G circuit board material in China.

**PCD&F** opened its 2021 New Product Introduction Awards for printed circuit board fabrication.

Z-zero signed an agreement for Mentor to distribute its Z-planner Enterprise padstack design software worldwide starting in July.

#### **CA** People

Escatec named **Patrick Macdonald** chief executive.

Intelligent Manufacturing Solutions (IMS) named **Jim Barry** director of business development. His experience includes 14 years as president of Eltek USA and seven years in executive positions at Strataflex.

Kimball Electronics promoted Steve Korn to president of Global Electronics Manufacturing Services Operations, and Lee Kemper to vice president of Diversified Contract Manu-

facturing Services.

Libra Industries appointed Trever Winters VP of operations at its Dayton, OH, facility. He has experience as master scheduler, supply chain analyst, and most recently site manager.

Moog named **John Hengst** SMT manufacturing engineer.

Mostafa Aghazadeh of Intel has been elected chairman of the iNEMI board of directors.

National Circuit Assembly named Wade Owens CFO. Owens brings more than 20 years of management experience in the financial and banking sectors.

Ning-Cheng Lee, Ph.D., VP of technology at Indium, and John Lau, Ph.D., CTO of Unimicron, have coauthored Assembly and Reliability of Lead-Free Solder Joints. The book covers Pb-free solder joints for advanced reliability across the food chain of electronics products.

SMTA announced Martin Anselm has been elected president for the term 2020-2022.

#### TestEquity named **Dan Stewart** chief marketing officer and **Nick Hawtrey** CFO.

VJ Electronix appointed **David Hamel** director of global sales and marketing. He joins VJ from Boston Semi Equipment, where he served as vice president of sales.

#### **Benchmark Adds Fab Shop in Phoenix**

**PHOENIX** – Benchmark Electronics has joined the ranks of vertically integrated manufacturers with its new 122,000 sq. ft. state-of-the-art factory in Phoenix. The end-toend process encompasses a dedicated design center, board fabrication, assembly and test, highlighted by a state-of-the-art factory 4.0 lights-out SMT line.

The plant, which houses a Benchmark Lark Technology team, as well as other Benchmark operations, celebrated its grand opening in June.

It is the fourth greenfield fabrication plant built in the US in the past 20 years, the others being Whelen Engineering's captive shop, which opened in 2015; GreenSource Fabrication, which launched in 2018; and TTM's new plant in Chippewa Falls, built in a converted 20-year-old, 40,000-sq. ft. warehouse and officially opened last winter.

Benchmark is the fifth-largest EMS company in the US and 18th in the world, according to the CIRCUITS ASSEMBLY Top 50.

The fab shop features automated plating for copper and final finish, laser-direct imaging (LDI) and an automated MSAP line capable of producing 1 mil (25 micron) lines and spaces. The company has two laser drills and two mechanical drills, with the lasers capable of microvias to 2 mils, while the mechanical drill capability is currently 6 mils, with the expectation it will reach 4 mils later this year. Sequential lamination processing is standard. Final finishes include ENIG, ENEPIG and EPIG. Benchmark can process a variety of laminates, including rigid, polyimide, BT, high-performance blends, LCP, PTFE, and mixed-material hybrid constructions. Legends are screened, with inkjet planned for later this year.

A big part of the site investment was the ISO 7 and 8 cleanrooms, adds Kevin Walker, product line director, RF & High Speed Circuits at Benchmark Lark. Inventory is kept in the cleanroom.

While the company had manual plating as part of its partnership with HSIO that started in 2018, the Phoenix plant upgraded to automated copper for direct plate and final finish for precision deposition control.

The MSAP process will enable size, weight, performance and cost (SWPC) improvements for many end-markets, with a focus on aerospace and defense customers, who are "enthusiastic supporters of what we are doing," said Walker.

The SMT area includes a volume production line, with an NPI line to be installed by the end of the year. Benchmark installed 3-D x-ray, Sonoscan micro-acoustic imaging, a laser confocal microscope for surface analysis, and performs microwave test up to 110GHz.

Daniel Everitt, vice president, Benchmark Lark, says the fab shop gives Benchmark "the opportunity to eliminate superfluous packaging, achieve high-reliability designs and performance for our customers, as well as mixed technologies where we mix an SMT and microelectronics assembly to create a hybrid module, which is commonly used in space, military and defense applications for the most highly demanding scenarios, as well as the highest reliability scenarios."

While Arizona is not a water-rich state, the shop has closed-loop treatment systems for air and water.

The site will build bare boards for both OEMs and other EMS companies. (MB)

#### IPC Releases New Press-Fit Connector Standard

**BANNOCKBURN, IL** – IPC announced the release of a new standard for the qualification and acceptance of press-fit technology. IPC-9797, *Press-fit Standard for Automotive Requirements and Other High-Reliability Applications* also includes high-reliability needs for automotive and other industries such as aerospace.

Press-fit technology is relatively new to the automotive industry and highreliability needs but not to electronics, IPC said. Used primarily in the telecommunications industry, the dependability and efficiency of press-fit makes it stable for use in high-reliability electronics.

The technology has been found to be critical to the manufacturing of electronic and electro-mechanical components. (CD)

# PCBCC

#### **Recent Chats:**

Kevin Walker on Benchmark Lark Technology's new fabrication/assembly plant

InspectAR on electronics debugging tools

Wally Rhines on the latest PCB design tools market trends

Christopher Tang, Ph.D. on supply chain changes in the Covid era

upmg.podbean.com

### The PCB Podcast

#### **CA Briefs**

A bipartisan pair of US senators have introduced a bill to restore semiconductor manufacturing to American soil by increasing federal incentives to stimulate advanced chip manufacturing, enable cutting-edge research and development, secure the supply chain and bring greater transparency to the microelectronics ecosystem.

ASE Technology, Powertech, SPIL and Amkor plan to take advantage of incentive schemes recently announced by the Indian government to set up semiconductor packaging and test services in the country.

Acer is seeing shortages of components, including passive components, ICs and panels by around 30% due to surging orders from the end-market, according to co-COO Tiffany Huang.

Adco Circuits has developed a free instant costing tool for circuit board assemblies that takes a bill of material and outputs a price with complete unit costs.

**AIM Solder** opened a stocking facility in Manaus, Brazil.

**Benchmark Electronics** will close its plant in Angleton, TX, in the first half of next year.

**Capital Partners** completed a control investment in **MicroCare** in partnership with the company's cofounder and senior management on May 28.

**Cascade Systems** is moving its EMS supply chains from China.

**Charles Edward Industries** plans to invest \$1.5 million in a new EMS plant in Asheville, NC, over the next three years.

**CheckSum** named **Horizon Sales** representative in Michigan, Ohio, Indiana, Kentucky, Western Pennsylvania, Illinois, Eastern Iowa, Wisconsin and Florida.

**CIRCUITS ASSEMBLY** is now accepting entries for the 29th annual Service Excellence Awards (SEAs) – the premier awards program in electronics manufacturing.

Cobham Advanced Electronic Solutions sold its radiation testing unit to Radiation Test Solutions.

**Critical Manufacturing** appointed **SDG** manufacturers' representative in Italy, Malta and Albania.

DataED and Bestronics announced a merger to form Emerald Electronics Manufacturing Services (Emerald EMS).

**Datest** is acquiring a second **Spea** 4060 flying probe tester.

**Dichaba Consumer Electronics** opened an electronics assembly facility at the Botswana Innovation Hub. **East/West Manufacturing** purchased a **Nordson Select** Cerno 103IL selective soldering system.

ECD has developed a five-module course that provides electronic assembly specialists with an overview of thermal profiling basics (ecd.com/electronics/courses/thermal-profiling-course/thermal-profiling-m0.aspx.).

**Enics** will open a 10,000 sq. m. highvolume electronics manufacturing facility in Senai, Malaysia, in early 2021.

**Foxconn** aims to improve its gross margin from a current 6% to 10% in 2025. It also set up its own research center to work on new technology, including 5G telecommunications, artificial intelligence and cybersecurity.

Foxconn is planning further investment in India and may announce details in the next few months. Foxconn, Wistron, Flex, Samsung, Oppo and Vivo are likely to apply for a production-linked incentive scheme (PLI) worth Rs 41,000 crore as part of India's massive push to wean away companies from China and emerge as the world's hub for electronics production.

Gentec purchased a MIRTEC MV-3 Omni 3-D AOI.

A smart manufacturing trial base in central Taiwan will progress from experimental production for components to technological verification of smart manufacturing solutions, according to the **Intelligent Machinery Technology Center**.

Johnson Outdoors installed a Nordson Dage Assure x-ray component counter.

KIC is integrating its profiling technology into SMT Thermal Discoveries' vacuum reflow oven and standard reflow machines. It also appointed Technical Marketing Company manufacturers' representative in Colorado, Utah and Idaho.

Lockheed Martin purchased an Austin American Technology X30-A vertical cleaning system.

The Manufacturing Technology Centre (pictured) has developed the first stage of Europe's first smart factory demonstration for the manufacture of electronics assemblies.

The MTC in Coventry, England.

**Nokia** became the first major telecom equipment maker to commit to adding open interfaces in its products that will allow mobile operators to build networks that are not tied to a vendor.

**Nordson Select** named **Fuji Do Brasil** sales representative for the Select product line throughout South America.

One Equity Partners will acquire the Sparton EMS business for an undisclosed amount from Cerebus Capital Management. The transaction is expected to close during the third quarter, subject to regulatory and customary closing conditions.

Out of the Box Manufacturing purchased a MIRTEC MV-6 Omni SPI.

**Pegatron** is renting a plant in Vietnam that will go online in early 2021, and **Qisda's** chief executive said the firm is constructing a new factory there as well. Pegatron will gradually boost its non-China production ratio to 10 to 20% by 2021.

Scanfil EMS is selling its subsidiary Scanfil (Hangzhou) Co. for €18.4 million to Hangzhou Cabinet Technology, a mechanics manufacturer.

**SMT Northwest** purchased a **MIRTEC** MV-3 Omni desktop 3-D AOI.

**TT Electronics'** Global Manufacturing Solutions division is opening operations in Kuantan, Malaysia, in response to customer demand for an additional manufacturing center in Asia.

Yamaha Motor Europe Factory Automation appointed Routeco distributor of industrial robots and associated controllers and accessories in the UK.

Z-Axis installed an ITW Speedline MPM/ SPM stencil printer and two updated Mycronic MY9E pick-and-place machines.

### **IPC CLASS 3 DESIGN GUIDE**

Introduction

$\otimes$

$\otimes$

$\otimes$

$\otimes$

$\otimes$

$\otimes$

$\otimes$

$\otimes$

$\otimes$

$\otimes$

- What is IPC?

- Class 1, Class 2, and Class 3 PCBs

- IPC Guidelines for Manufacturing Defects

- IPC Standards for Annular Ring Design Rules for Annular Rings

- IPC Standards for Assembly Process

- IPC Standards for Solder Joints

- Common Differences Between IPC Classes

- PCB Cross-Section Verification

- IPC Documents to Set the Level of Acceptance Criteria

#### EDITED by CHELSEY DRYSDALE

| CALM BEFORE THE STORM?                                                                                                                                            |      |               |      |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|-------|

| Trends in the U.S. electronics<br>equipment market (shipments only).                                                                                              |      | % CHA<br>Apr. |      | YTD%  |

| Computers and electronics products                                                                                                                                | -0.7 | 0.5           | 0.5  | 0.9   |

| Computers                                                                                                                                                         | -4.1 | -0.2          | 0.7  | -12.6 |

| Storage devices                                                                                                                                                   | 0.2  | -2.8          | -0.2 | 57.4  |

| Other peripheral equipment                                                                                                                                        | -3.2 | 2.8           | 9.4  | 5.2   |

| Nondefense communications equipment                                                                                                                               | 2.9  | -0.2          | 0.9  | 5.8   |

| Defense communications equipment                                                                                                                                  | 0.4  | 3.5           | 3.4  | -3.7  |

| A/V equipment                                                                                                                                                     | -8.4 | 5.3           | 1.4  | -19.0 |

| Components <sup>1</sup>                                                                                                                                           | -0.9 | 1.9           | 0.8  | 8.8   |

| Nondefense search and navigation equipment                                                                                                                        | -1.3 | -1.3          | -0.9 | -6.5  |

| Defense search and navigation equipment                                                                                                                           | 0.0  | 0.3           | 0.2  | 3.5   |

| Medical, measurement and control                                                                                                                                  | -0.9 | -1.1          | 0.0  | -4.1  |

| <sup>1</sup> Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted.<br>Source: U.S. Department of Commerce Census Bureau, July 2, 2020 |      |               |      |       |

| US MANUFACTURING INDICES                              |      |      |      |      |      |

|-------------------------------------------------------|------|------|------|------|------|

|                                                       | FEB. | MAR. | APR. | MAY  | JUN. |

| PMI                                                   | 50.1 | 49.1 | 41.5 | 43.1 | 52.6 |

| New orders                                            | 49.8 | 42.2 | 27.1 | 31.8 | 56.4 |

| Production                                            | 50.3 | 47.7 | 27.5 | 33.2 | 57.3 |

| Inventories                                           | 46.5 | 46.9 | 49.7 | 50.4 | 50.5 |

| Customer inventories                                  | 41.8 | 43.4 | 48.8 | 46.2 | 44.6 |

| Backlogs                                              | 50.3 | 45.9 | 37.8 | 38.2 | 45.3 |

| Source: Institute for Supply Management, July 1, 2020 |      |      |      |      |      |

| KEY COMPONENTS                                                                                                                                                             |        |       |       |                    |                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|--------------------|--------------------|

|                                                                                                                                                                            | JAN.   | FEB.  | MAR.  | APR.               | MAY                |

| Semiconductor equipment billings <sup>1</sup>                                                                                                                              | 22.7%  | 26.6% | 20.1% | 18.2% <sup>r</sup> | 13.1% <sup>p</sup> |

| Semiconductors <sup>2</sup>                                                                                                                                                | -0.35% | 5%    | 6.85% | 6.13% <sup>r</sup> | 5.84% <sup>p</sup> |

| PCBs <sup>3</sup> (North America)                                                                                                                                          | 1.05   | 1.15  | 1.15  | 1.19               | 1.10               |

| Computers/electronic products <sup>4</sup>                                                                                                                                 | 5.42   | 5.41  | 5.43  | 5.44 <sup>r</sup>  | 5.43 <sup>p</sup>  |

| Sources: <sup>1</sup> SEMI, <sup>2</sup> SIA (3-month moving average growth), <sup>3</sup> IPC, <sup>4</sup> Census Bureau, <sup>p</sup> preliminary, <sup>r</sup> revised |        |       |       |                    |                    |

#### Hot Takes

- The worldwide contract manufacturing services market increased 2.5% year-over-year in total revenue to \$555 billion. The EMS/ODM market expanded \$13 billion from 2018. For the 10th year in a row, the CM industry was profitable, at \$6.8 billion (for 34 EMS public companies and 17 ODM public companies), decreasing by \$900 million from 2018. Foxconn accounted for more than half of all the earnings of the EMS industry in 2019, at \$4.3 billion. (New Venture Research)

- PCB sales among German, Austrian and Swiss fabricators rose 16% sequentially in the first quarter but fell 7.5% year-over-year. (ZVEI)

- The Covid-19 pandemic effect on numerous end-products slowed the growth rate for HDI in the first quarter. Taiwanese high-end HDI makers suffered relatively minor impact, however, as the HDI sector grew 7.5%. (TPCA)

- Worldwide spending on the Internet of Things (IoT) has been significantly impacted by the economic effects of the

Covid pandemic, although a back to double-digit growth rebound is expected both in the mid- and long-term. (IDC)

- Memory spot prices, particularly for DRAM, have started to rise, reflecting a pickup in buying momentum prior to China's 618 shopping festival.

- The AR/VR/MR industry is predicted to top \$30 billion by 2030, in part from an uptake of devices for use in everyday life. (IDTechEx)

- Vendor revenue in the worldwide server market declined 6% year-over-year to \$19 billion during the first quarter. (IDC)

- 2021 is poised to mark a banner year for global fab equipment spending with 24% growth to a record \$68 billion, 10% higher than the previously forecast \$66 billion. (SEMI)

- Exports by the German electronics industry in April plummeted 20% compared to the previous year to 13.5 billion euros. (ZVEI)

#### Covid-19 has Forced Us to Change. Will It Stick?

We must retain our new agility even after the pandemic ends.

NOTHING MAKES YOU flexible like a crisis. Yet, as rough as it can be for a person to quickly shift gears, it is significantly more daunting for a corporation to do so.

The entirety of my working career, the mantra of any good business consultant or culture guru has been be flexible and embrace change. Whether an organization is implementing a TQM (total quality management) plan or struggling with financial survival because "plan A" no longer works, embracing flexibility and rapid change is never easy – and often unsuccessful. The larger the organization, the harder it can be. Embracing change and becoming flexible often only occurs when no other option remains, or in short, extinction awaits.

In these most unusual times of Covid-19, however, most people and virtually every company have been forced to embrace radical change overnight. Some change is cultural. To wit: Where employees work and how they communicate has stretched some companies much further than they could have imagined a few short months ago. For instance, large, centrally located staffs have reconstituted in home offices. Restaurants now are embracing outdoor seating and simplified, modified menus. And everyone, in one form or another, has become more open to wearing masks, shopping following in-store traffic patterns, and greeting friends with elbows rather than handshakes. All this change has been rapid, requiring flexibility of thought and action.

As extraordinary as these cultural changes are, some large corporations have demonstrated they can make an elephant dance. Indeed, the ability of some companies so rigid they have the flexibility of a steel I-beam, in industries that traditionally take years to "change," has radically changed what they produce to support the common good of fighting Covid-19 virtually overnight.

The auto industry has a deserved reputation for moving relatively slowly. It typically takes years for an automaker to develop new technology, tool it and produce it. However, Ford and GM, companies not known for producing medical equipment, rapidly converted manufacturing facilities, bringing them up to medical standards (read: cleanroom environment), tooled, and are successfully producing ventilators. Fiat-Chrysler was not left out; they produced many of the parts that go into ventilators made by Ford, GM and others. If these industrial behemoths can show the flexibility and the appetite for such radical change, imagine if they harness those traits when rolling out the next generation of automobiles. They are not alone. Bacardi, Brown & Forman, and LVMH – companies known for their spirits and wines – have entered the hand sanitizer business. These companies, as well as cosmetic companies such as L'Oréal, have shifted gears to new, very different product lines and rapidly scaled to volume production.

S.C. Johnson and Dow, two major chemical companies with a good number of overlapping/competitive products, started to work together to produce hand sanitizers and wipes in volume to stock medical facilities and home consumers. Competitors working together with employees who have the flexibility to shift production and share technical data again demonstrates how rapid change can be.

Face mask production has been the catalyst for virtually every clothing company of late. A corporate neighbor of mine is a supplier to Brooks Brothers, the high-end clothing store. It converted a factory for making shirts into one for masks over a weekend. Other clothing suppliers, which served everyone from high-end boutiques to Walmart, rapidly and successfully converted manufacturing to masks and medical garments. Whether homemade over a kitchen table or produced in mass by a large clothing manufacturer, countless people and businesses embraced change and demonstrated flexibility.

Our electronics industry always needs to be nimble and flexible, as the technologies we are involved with constantly change. Our usual rate of change is nothing compared with what's required to fight a pandemic, however. With scores of electronics firms now producing medical equipment and ventilators, and so many in their supply base providing the chemicals and raw materials necessary to get the job done, ours is among the markets embracing real change.

A vast majority of people and companies across the globe have had to react to the realities of this pandemic. Flexibility is the common trait we have all embraced. Change, painful as it is at times, is the desired result of exercising flexibility. When our lives finally return to a semblance of normal, however, which companies or industries will leverage the lessons learned and adapt them into their corporate culture – their business approach – for competitive advantage?

We have all been witness to sudden and rapid change, and our flexibility has been exercised and stretched. Those who take to heart the advantages that can be realized by staying nimble, being flexible, and embracing – rather than avoiding – change, personally as well as throughout the organization, have the best chance of long-term success.  $\Box$

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

#### The Covid-19 Sales Challenge

With travel frozen, rethink and repurpose those marketing dollars.

BY MAKING FACE-TO-FACE sales calls impossible, Covid-19 is challenging electronics manufacturing services (EMS) salespeople to work in new ways. Sadly, that challenge isn't likely to go away soon. On the bright side, it opens the door to a more productive, less costly sales and OEM relationship, provided salespeople modify their approach.

In the normal flow of EMS selling, there is typically a lead follow-up phase that results in a face-to-face sales call. There may be an additional meeting to present a quotation, depending on the distance between

the salesperson and decision-maker. There is also usually a plant tour. When all these activities are local, costs drop to the amount of time the individuals spend on the activity. However, the cost of a sales call that involves business travel may be \$1,000 to \$2,000, depending on mode of travel and how many sales calls are clustered into that trip.

In the era of Covid-19,

most companies are significantly limiting sales calls. The ability to reduce the cost of a sales call by visiting several companies at once is no longer doable. Salespeople who focused primarily on showing up hoping to get an appointment aren't even allowed in the lobby. Many companies are also restricting employee travel, which means plant tours aren't happening. An added challenge is employees who can work at home are encouraged to work at home, which makes prospects harder to get on the phone.

Therefore, salespeople need to work smarter to both open the door to opportunities and close the sale with a plant tour. Here are a few suggestions on how to creatively approach this challenge:

- Evaluate the contacts in your prospect database. Covid-19 has changed the sourcing strategy playing field, and OEMs have different criteria now. Companies that weren't interested in your EMS company six months ago may be now. Additionally, the prospects in that database have some level of preexisting relationship, which makes opening the door a little easier.

- Remind the prospects in your database you are out there. The rules about mindshare maintenance haven't changed. OEMs will focus on the EMS companies that stay in touch with them.

- Tie your messaging to points of pain. What is likely

to keep prospects up at night in a Covid-19 world? Closed factories, resource shortages that delay deliveries and challenges in transferring production are likely to be the top three. Build your message around your company's ability to solve those challenges.

Create a Skype plant tour. While some OEMs may be happy with a marketing video alone, convincing them to take a plant tour via Skype will enable your team to build a relationship during that tour. However, having someone in the plant wander around with a smartphone is likely to be a disaster. So, create

> a repeatable format and use someone capable of providing strong visuals and talking the prospect through the tour. Do a dry run before doing it with a prospect to make sure the right person conducts the tour. Keep reasonable time limits, show the right areas of the factory, and point the phone in the right direction.

Listen to your prospects. Everyone is navigating Covid-19 challenges. What parts of their sourcing analysis process are they having difficulty doing right now? Can your team develop a "virtual" way to provide the answers they need? Every time you help a prospect solve a challenge, you build a stronger relationship.

These are the times that test salesmanship skills. Salespeople with a consistent approach that builds off a network of contacts will navigate Covid-19 challenges. If travel is not an option, consider repurposing part of that budget into lead-generating marketing activities. The entities that normally have trade shows have switched to webinars and other virtual networking venues, so there are opportunities to rethink marketing activities. Consider creating short podcasts or videos that involve conversations with your company's technical resources on issues they've solved for customers for distribution via social media. In short, figure out creative ways to do the things virtually that you used to do face-to-face.

We are looking at a challenge that will likely change the way sales are done for the next year. Pivoting to virtual solutions earlier will open the door to more opportunities and position your company as a creative problem-solver. SUSAN MUCHA is president of Powell-Mucha Consulting Inc. (powellmuchaconsulting. com), a consulting firm providing strategic planning, training and market positioning support to EMS companies and author of Find It. Book It. Grow It. A Robust Process for Account Acquisition in Electronics Manufacturing Services: smucha@powellmuchaconsulting. com

"If travel is not an option, repurpose part of that budget into **lead-generating marketing**."

# Understanding High-Speed Constraints

### FREE new e-book!

pcdandf.com/pcdesign/constraints

This fabulous treatise allows PCB designers and engineers to understand all the important constraints and determine their values.

written by\_ Charles Pfeil

Charles Pfeil has spent over 50 years in the PCB industry as a designer, owner of a service bureau, and in engineering management and product definition roles at Racal-Redac, ASI, Cadence, PADS, VeriBest, Mentor Graphics, and Altium. He was the original product architect of Expedition PCB.

#### Generating PCB Footprints for Your First Layout

And why your library naming convention should be memorable.

AS A DESIGNER who has put himself into the public eye, a lot of questions come my way. Several beginners have approached me with basic questions I can usually answer by sharing something I've already written. Sometimes I'll end up writing a few paragraphs that eventually expand into a column to share with everyone. One gentleman, whom I will call Aakash, has leaned on me so many times I think he might be compiling a book. The messages pile up, as do the answers. Let's get to one of those types of answers.

et's get to one of those types of answers

More than one person has asked about starting their first job going from the ground up. "How do I make all the parts I need for my first board?" The short answer is to build them one at a time. This is the internet age. This is the 21st Century. There must be a better way! It's not that we're impatient; we just don't have that kind of time. Software vendors know that, and the internet does too. The software installation comes with a bevy of common parts, but most boards go well beyond the generic SMD capacitors and resistors found in the default library.

You have it so good. In "my day" we finished a layout and saved it to a floppy disk. We walked it over to Document Control, and they put it in a file cabinet. Some veterans may be nodding. For you kids, a floppy disk looks like the icon we use for saving our designs, but that's a story for another time. Now get off my lawn!

The library must start somewhere, and most PCB layouts start

FIGURE 1. The PCB layout can only be as good as the underlying footprints all the way down to the padstack where it all begins.

FIGURE 2. One of the most common SMD packages is the QFN, quad flatpack no lead, as opposed to QFP, which has gull wing leads protruding from the body. Credit: Reference Designer.

at the connector, so I'll start there. Connectors are like snowflakes, more or less by design. You can find at least 100 different circuits that fit on a QFN-16. That's a square with 16 pins spaced maybe a half a millimeter apart with a center ground pad. Meanwhile, every connector mates to only one other connector. An SMA connector doesn't work with an SMB socket. Why connector catalogs are so byzantine. Worries

over patent infringement and protecting their turf work against the connector vendors. I don't expect them to ever standardize on the particulars. The proliferation of connectors is further complicated by the way connectors are documented. You will never find a drawing of the connector you need. What you will find is a representative image used for the entire connector family. Everything from two pins to 300 is represented by that single drawing. Then you get to decode the part number to find the actual body dimensions. Up to 17 pins, it's one row, 18 to 80 is two rows, then three and so on (FIGURE 3). Turn to some other page that indicates what the plating letter means. Another table breaks down whether there are zero, one, two or more alignment pins. Go to still another page to find out if your mating connector locks down mechanically or relies on friction. Do you want tape-and-reel? Or is a tray okay?

JOHN BURKHERT JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for highspeed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly.

Coming to this from the component selection side is the same thing in reverse. You build that part number one character at a time. When finished, you get to contact the vendor to see if it is a standard part or if you get to wait six weeks and pay some nonrecurring engineering fees. Maybe you have to roll the dice again. All for the pleasure of buying some connectors. I just love connectors, and they're on almost every board. I'll try capacitive charging with an array of antennas and still get a swath of board-to-board connectors.

A brief history on library generation. Back in the era of floppy disks, I had catalogs from Amp, Samtec and others to suss out the details. The best ones were from Texas Instruments. One fine day, a new PCB designer rolled into an empty space we called a "cubicle." As he unpacked his box, I couldn't help but notice a large number of UPS-Brown

FIGURE 3. The 2020 Hirose pamphlet. If you want to build the part, be ready to turn some pages.

| COMPONENT, CATEGORY                                              | LAND PATTERN NAME                                               |

|------------------------------------------------------------------|-----------------------------------------------------------------|

| Thin Quad Flat Packages, 0.50 mm Pitch, Height s 1.60 mm         | TSQFP50P + Lead Span L1 X Lead Span L2 Nominal - Pin Qty        |

| Thin Quad Flat Packages, 0.40 mm Pitch, Height < 1.60 mm         | TSQFP40P + Lead Span L1 X Lead Span L2 Nominal - Pin Qty        |

| Thin Quad Flat Packages, 0.30 mm Pitch, Height s 1.60 mm         | TSQFP30P + Lead Span L1 X Lead Span L2 Nominal - Pin Qty        |

| Ceramic Quad Flat Packages, 1.27 mm Pitch                        | COFP127P + Lead Span L1 X Lead Span L2 Nominal - Pin Oty        |

| Ceramic Quad Flat Packages, 0.80 mm Pitch                        | COFP80P + Lead Span L1 X Lead Span L2 Nominal - Pin Qty         |

| Ceramic Quad Flat Packages, 0.635 mm Pitch                       | COFP63P + Lead Span L1 X Lead Span L2 Nominal - Pin Oty         |

| Quad Flat No Lead Packages 0.80 mm Pitch QFN8                    | OP - Body Width X Body Length in Metric - Pin Qty + Thermal Pad |

| Quad Flat No Lead Packages 0.65 mm Pitch QFN6                    | SP - Body Width X Body Length in Metric - Pin Qty + Thermal Pad |

| Quad Flat No Lead Packages 0.50 mm Pitch QFN5                    | OP - Body Width X Body Length in Metric - Pin Oty + Thermal Pad |

| Quad Flat No Lead Packages 0.40 mm Pitch QFN4                    | OP - Body Width X Body Length in Metric - Pin Qty + Thermal Pad |

| Quad Leadless Ceramic Chip Carriers (JEDEC Standard Packag       | e) LCC + Body Width X Body Length in Metric - Pin Oty           |

| Quad Leadless Ceramic Chip Carriers (Pin 1 on Side)              | LCCS + Body Width X Body Length in Metric - Pin Qty             |

| Quad Bottom Chip Carrier (JEDEC MO-2178)                         |                                                                 |

| Resistors, Chip                                                  | RESC + Body Size in Metric                                      |

| Resistors, Chip, Array                                           | RESCA + Pitch P + Body Width X Body Length in Metric - Pin Qty  |

| Resistors, Molded                                                | RESM + Body Size in Metric                                      |

| Resistors, MELF                                                  |                                                                 |

| Small Outline IC, J-Leaded 300, 350, 400, 450 mil Body Width (P  | itch 1.27 mm) SOJ127P + Lead Span Nominal - Pin Oty             |

| Small Outline IC, J-Leaded (Pitch 0.65 mm)                       | SOJ65P + Lead Span Nominal - Pin Qt                             |

| Small Outline Integrated Circuit, 1.27 mm Pitch (Standard 50 mil | Pitch SOICs) SOIC127P + Lead Span Nominal - Pin Qty             |

| Small Outline Packages, 1.27 mm Pitch (Nonstandard 50 mil Pitc   | h SOICs) SOP127P + Lead Span Nominal - Pin Qt                   |

| Small Outline Packages, 1.00 mm Pitch                            | SOP100P + Lead Span Nominal - Pin Qt                            |

FIGURE 4. IPC-7351B gives a flavor for how to create footprints searchable by their parameters.

paperbacks that were all identical except for minor variations in width. He owned the entire Encyclopedia Motorola! I didn't even know his name, but I already liked him. Those items were a status symbol to me at least. My generation got tired of lugging all those books around, so we invented the internet.

That's where you come in. Do you want to slog through those books and piece together a component footprint one padstack at a time? Ask your vendor(s) if they can part with more than a .pdf file and provide a CAD file in your preferred format. Some will offer files for a specific ECAD tool or a STEP model to import. Others may be old school and deal only in .dxf files. Either way, you have a leg up on starting from scratch with the "wizard." Verifying the right geometry is still up to you.

Library naming conventions. No matter how you approach library generation, a naming convention is a must. As your library grows, it's possible to spend more time browsing for an existing part than it would take to build it again. IPC-7351 to the rescue. Each revision of this document goes into a little more depth to cover the millions of different footprints and the various ways they will be built.

Circling back to the QFN, a typical file name is as follows: QFN50P\_300x300\_16\_150x150. The newer revision of the document will include another character or characters to define the footprint in greater detail. The point is to stick to a system. If you're starting with chaos for file names, then you want to make renaming your symbols part of each design effort, one board at a time. Twenty percent of the parts cover 80% of the board, so it gets easier as you go.

IPC-7351B, page 17, gives a flavor for how to create footprints in such a way they can be searched by their parameters (**FIGURE 4**). One of the most important characteristics is footprint size: small, medium or large. For everything

but Class 3 high-reliability work, I recommend the nominal size, rather than over- or undersize footprints. If big pads present an impedance issue, or the boards are very high-density, it could be useful to minimize size. The Ghostbusters tell us to "never cross the streams"; I'm telling you to never mix the minimum, nominal and maximum size component footprint types. Bad things can happen if you commit either of those sins on the same board, especially with the same part.

It doesn't take a hero to curate a good library. Help is available. A number of companies will generate library parts by subscription or piece-

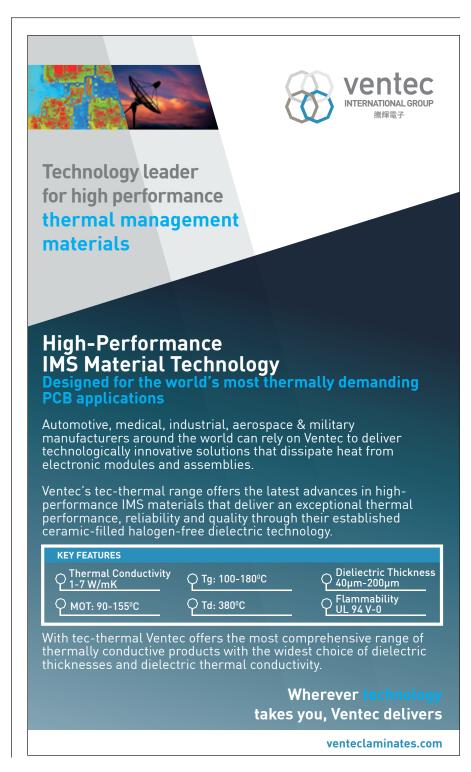

### Reliability Needs to be Designed-In from the Lowest Level

Cutting-edge technology demands more care to ensure reliability and resilience.

HUMAN NATURE IS to invent, to create technological solutions to the challenges and problems we see. We are increasingly dependent on high-technology solutions as we address more complex issues. Some of these issues are of our own making. Others arise from our increasing expectations: what we want to do, where we want to go, how safe we want to feel.

All this keeps the electronics industry extremely busy. And the equipment we create – remote smart sensors, street-level broadband infrastructure, full-color digital signage, supercomputers on wheels (or wings) – is more and more likely to be required to operate faultlessly in extreme environmental conditions. Gone is the era when advanced electronics assemblies were mostly destined to spend their lives in air-conditioned telecom offices or otherwise benign environments. Now, they are out in the cold. And the heat. And the humidity. And this presents a major reliability challenge that needs to be addressed at every level from the installation and the enclosure down to the substrate.

The effects on components caused by environmental factors such as high ambient temperatures and humidity can be obvious, often manifested as surface oxidation, corrosion, or mechanical distortion. Excessive heat can quickly dry wet electrolytic capacitors, which consequently lose their capacitance over time. The properties of substrate materials also can be liable to change with exposure to environmental factors such as moisture, as well as due to general aging. Substrates exposed to excessive humidity can absorb moisture, which increases the dissipation factor (Df), leading to more lossy behavior that saps signal energy.

Conductive anodic filament (CAF) formation is another phenomenon that gets attention within the industry, although we still have lengths to go to address the issue rigorously and properly. Still often considered a material issue, CAF performance is known to be influenced by design and process, in addition to temperature, humidity and bias. Pathways are also essential for CAF progression. As package I/O pitches continue to shrink, and component placement density continues to increase, these trends are moving against efforts to maximize reliability.

Initial observations of CAF were restricted to laboratory testing. Now, however, we are pushing equipment containing extremely densely populated boards into the field, and it needs to stand up to the environment. Recent trends in e-mobility have also moved CAF performance requirements from tens of volts to thousands of volts, bringing very real challenges in test design and equipment use.

Another modern trend is a large proportion of remotely installed equipment can be considered mission-critical. So many of us are dependent on mobile and Internet-based services to work, do our banking, authenticate our identities, and host our wallets and travel credentials, such as train tickets and aircraft boarding passes, that our world would grind to a halt if we couldn't rely on the infrastructure and sensors distributed liberally throughout the places we go. And this is without mentioning our reliance on automotive safety features and the roadside and trackside technology that support services such as signage and signaling. Looking ahead to when 5G becomes part of the mix of technologies involved in directing autonomous vehicles and remotely managing industrial automation, its capacity for massive machine-type communications (mMTC) and ultra-low-latency communications (ULLC) must come with assured reliability.

In addition, despite clear economic arguments for standardizing hardware across multiple product lines, addressing different applications and different markets, design teams should assess whether an assembly will be reliable when taken out of one context and placed in another. There is an increased tendency to create software-defined products based on a common hardware platform. While this can allow flexibility to address the needs of different markets, hardware must be designed to withstand the harshest conditions it is likely to encounter in any location it may be used. We need to be careful not to send assemblies into environments they were not designed for, in the interests of ease or financial expediency. Recall early failed attempts to migrate low-cost consumer electronics hardware to the automotive environment.

It may be relatively unexciting compared to the science-fiction lifestyles we can foresee coming within our reach. However, reliability is an issue that urgently needs to be addressed. To continue packing more components onto boards, with increasingly highdensity interconnects, and continue adding features and raising system capabilities, reliability needs to be designed in from the lowest level – the properties of the substrate material – upwards.

Materials suppliers should be careful to ensure new products are tested fully. This must include properly assessing long-term reliability, such as through thermal aging tests. This can be especially important ALUN MORGAN is technology ambassador at Ventec International Group (ventec-group. com); alun.morgan@ ventec-europe.com.

continued on pg. 28

# Are you getting to the bottom of your via?

Prevent connection failures in thick PCB substrates with plasma treatment

New VIA<sup>™</sup> Series 2.5 cleans deep, narrow vias where other processes can't go

Contact us now to learn more +1-925-827-1240 / info@nordsonmarch.com

nordsonmarch.com

VIA<sup>™</sup> Series 2.5 Plasma System

#### How to Really Read a Technical Roadmap

It might be factually correct, while also being completely impossible.

QUESTION: I AM looking to add a flex circuit supplier to our vendor base and requested its technical roadmap. After review, it appears almost exactly as the two vendors we currently have. Is this a coincidence, or do most (or all) flex suppliers have the same technical capabilities?

A technical roadmap is basically a document that outlines what a company can and cannot do from a technical standpoint (e.g., minimum trace/space, layer count, pad and via size, overall circuit size, etc.). I have never been a fan of technical roadmaps. Virtually every flex (and rigid) PCB supplier is compelled by their customer base to provide their capabilities, and therefore also their limitations. The problem with roadmaps is twofold. First, every supplier advertises the absolute best it has ever done in every single category. This is true even if it only did it one time, on one circuit, and in a beaker. This is not a fair representation of what the fabricator can or cannot do on production quantities. The second problem is the real answer for what a supplier can or cannot do is "it depends." Let's look at a few examples.

Trace/space feature size. Most flex suppliers will advertise their minimum trace/space feature size at  $50\mu$ m to  $75\mu$ m. But these numbers are meaningless without also knowing what copper thicknesses were used to establish these limitations. If they were able to etch  $50\mu$ m to  $75\mu$ m features on  $9\mu$ m or  $12\mu$ m copper, I say welcome to the club. If they did these feature sizes on 2+ oz copper, they have something to brag about. Unfortunately, this important detail is often missing from roadmaps.

is senior application engineer at Flexible **Circuit Technologies** (flexiblecircuit. com); mark.finstad@ flexiblecircuit.com. He and co-"Flexpert" NICK KOOP (nick. koop@ttmtech. com) welcome your suggestions. The authors will speak on flex design and manufacture at PCB West Virtual 2020 in September (pcbwest.com).

**MARK FINSTAD**

Via/pad sizes. It is practically industry standard that any supplier with a laser drill can form 75µm to 100µm blind vias and hit 250µm pads. But what happens when the circuit size increases to where the dimensional instability of the flexible material starts to wreak havoc on the locations of those vias? Drilling and imaging equipment with scaling capabilities certainly helps, but to be really beneficial, they need to be used in conjunction with sequential lamination construction. Depending on the number of lamination steps, a price tag is associated with that capability.

Layer count. As layer count increases, so does the importance of very high etching yields on internal layers. Consider the following example. Say you have an eight-layer circuit, and the supplier can get eight parts per panel. In this example, let's say your supplier averages one etching reject per layer. Theoretically, there will be panels where they may not get a good part. Murphy's Law dictates the internal etching rejects will be randomly placed on each layer and will almost never line up at a single circuit location. So, maximum layer count is a function of the feature sizes on each layer in the circuit. The smaller the feature sizes, the lower the etching yields. The more layers in the stack that have these small features (i.e., non-plane layers), the lower the overall yield. And as you probably guessed, the lower the overall yield, the higher the price.

Circuit size. This is one of my personal favorites. Most flex suppliers have at some point built relatively long (22" to 24") circuits. These are typically just one or two layers and have relatively large features. This is where proclaimed maximum circuit size on the technical roadmap can come back to bite you. Since you have indeed made a circuit 24" long, you include that on the technical roadmap. No problem, right? Then you get a Gerber package to quote where you find a 24" long and 5" wide six-layer circuit filled with 50µm lines/spaces on four of those layers. You contact the customer to let them know you will have to no-bid, and they may have difficulty finding a source anywhere that can support the application. The inevitable reply: "But the technical roadmap on your website shows this is within your capabilities."

Each feature on a technical roadmap is a standalone statement of that one capability only. When you mix and match these leading-edge capabilities, all bets are off. Again, I am not a fan of technical roadmaps because they are not indicative of the true capabilities of a supplier, or the supplier's ability to stack multiple challenging features into a single design. Rather than relying on a published technical roadmap where you can learn about the best a supplier has done, give your flex vendor a call and provide them with a two-minute "big picture" scope, including the important details. Most vendors will be able to tell quickly if you are on the right track or wandering into never-never land. □

### Look Inside. Datest does. Nondestructively. And beyond printed circuit boards.

A CT scan can tell you what's inside, what's not working, and set you on a path to correction. Fast.

Images tell a lot, if you know where to look, and what you're looking at.

Test Engineering. Failure Analysis. Answers.

47810 Westinghouse Drive • Fremont, CA 94539 Phone: 510-490-4600 • Fax: 510-490-4111 Email: info@datest.com • Website: www.datest.com

## Why Not ROUTE TWO TRACES Between Pins on a 1mm Pitch BGA?

A look at the geometry associated with plated through-holes in a PCB. **by LEE RITCHEY**

Application notes describe how to save layers in a PCB by routing two traces between pins on a 1mm pitch BGA. A leading FPGA vendor recommends this practice to use its very-high-pin-count FPGAs in a low-layer-count PCB. When this approach is used for a high-layer-count PCB, the result is often, if not always, very poor yields, and the board is unreliable when used in a system under actual conditions, as opposed to in a laboratory or a prototype built in a small volume by a specialty shop. The following discussion will illustrate why this approach results in unsatisfactory yields when volume manufacture is attempted.

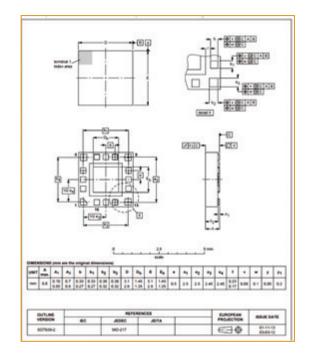

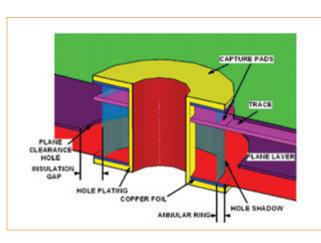

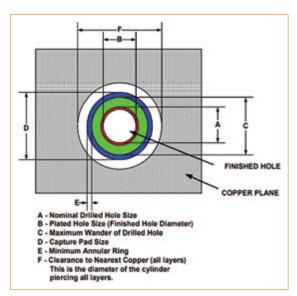

To understand the space used to route traces in signal layers of a multilayer PCB (this also applies to four-layer PCBs), it is useful to look at how plated through-holes (vias) are created and the various requirements that must be met by the finished PCB. **FIGURE 1** is an illustrated cutaway of a plated through-hole showing signal and plane layers.

Deciding the dimensions of the features in this diagram is often called padstack design. (This subject is discussed at length in Ritchey.<sup>1</sup>) The elements in a padstack design are the adequate copper bonding between traces and the plating in the hole.

As will be seen, the dimensioning involved in designing padstacks is done from the edges of the drilled, plated hole to features inside the PCB or the drill size. Traditionally, the PCB design process begins with the diameter of the finished plated through-hole. The choice of drill size has been left to the PCB fabricator, and the size of clearance holes and capture pads in signal layers is large enough for ample room for a range of drill sizes. As the pitch between device pins has shrunk over the years, this practice has resulted in PCBs with poor manufacturing yields.

To solve this problem, the designer of the PCB padstacks must take charge of specifying the drill size, as well as the finished hole size. To get from finished hole size to drill size, one need only to take the finished hole size and add 4 mils (0.102mm) to the finished hole size. Then, designing the padstack can proceed from the drill size. (Once these dimensions are chosen, the drill size must not be changed. If the drill size is made smaller than that specified, the aspect ratio may

finished hole size, the drilled hole size, the size of the capture pad in a signal or surface layer used to connect to traces and component leads, and the size of the clearance hole or antipad in the plane layers. Things to account for are minimum thickness of copper plating in the hole, allowance for drill wander in the fabrication process, allowance for misregistration between layers of the PCB, minimum insulation thickness between plating in the hole and metal in the signal and plane layers, and

**FIGURE 1.** An illustrated cutaway of a plated through-hole in a PCB.

grow too large, and plating may not be completed all the way through the hole. If the drill size is too large, the clearances to copper in adjacent layers may be too small, or the drill may break out the side of the capture pad on a signal layer.)

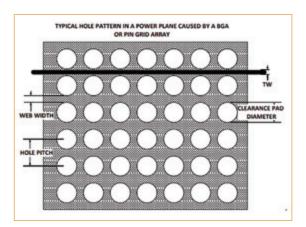

FIGURE 2 is a top-down view of a plated throughhole or via showing the clearance hole or pad in a power plane of diameter F. This is the minimum opening in the power planes needed to guarantee enough room for the drilled hole, the drill wander, and minimum insulation to the nearest copper in any layer, be it signal or power. **FIGURE 3** shows an array of vias or holes spaced on a 1mm pitch. The web between clearance pads is what is available for traces on signal layers and for copper in the plane layers to conduct the current used by ICs and other devices on the PCB. (Note: If the trace width is the same as the web in the plane, the impedance of the trace raises several ohms as it passes over the array of holes under a BGA. To minimize this effect, the web should be wider than the trace

by about 2:1.)

#### Calculating Width of Plane Webs and Routing Channels in Signal Layers

Clearly, the width of a plane web is the hole pitch minus the diameter of the clearance pad or hole. The question is how to arrive at the diameter of the clearance hole needed to satisfy all the constraints. These constraints are a drilled hole large enough to ensure proper plating; room around the drilled hole to allow for drill wander; and minimum insulation thickness.