pcdandf.com circuitsassembly.com October 2020

**6 WAYS TO ID COUNTERFEIT PARTS** *And 1 Question Why We Still Have To*

**Embedded Clearance on Flex Circuits**

Should BGA and CGA Packages be *Bigger?* Design for *Rework*

Supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credie during a supplies inspection governies avoid lievices criteria credies avoid cred

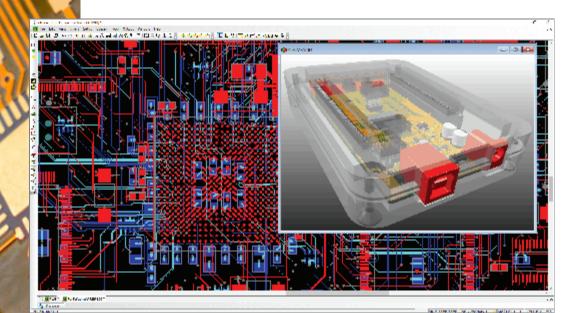

# Pulsonix PCB Design Software PCB design done right

# **Maximum Productivity in Minimal Time**

With a modern, easy-to-use interface and advanced capabilities to automate your layout process, Pulsonix can be the key to a critical reduction in your design time. That's PCB design done right!

# **Advanced PCB Design Features**

- Intuitive placement and routing

- Dynamic copper pour

- Full rules engine for automatic DRC

- High-speed design rules

- Heads-up display length matching

- Rigid-Flex, embedded components, and chip-on-board

- Revision control and PLM integration

Try Pulsonix yourself at pulsonix.com/trial

# PROTOTYPES IN 4 DAYS FROM TAIWAN

# **No Tariffs!** Best Quality and Price!

# Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

# Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

# ACCUITECOINC. SINCE 1986

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015

# FIRST PERSON

# 6 CAVEAT LECTOR

Driving out the fakes. Mike Buetow

# MONEY MATTERS

#### 15 ROI

Meeting of minds, if not bodies. Peter Bigelow

#### 16 FOCUS ON BUSINESS

Covid has been the ultimate organizational stress test. Susan Mucha

### 18 BETTER BOARD

No service, no customer. Greg Papandrew

# TECH TALK

#### 20 DESIGNER'S NOTEBOOK

A robust design will lend itself to touch-up and rework. John Burkhert

#### 21 MATERIAL GAINS

Research for research's sake. Alun Morgan

#### 22 THE FLEXPERTS

Embedded clearance. Nick Koop

#### 42 SCREEN PRINTING

Long live the stencil! Clive Ashmore

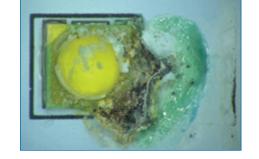

# 44 DEFECT OF THE MONTH Solder joint corrosion causes. Bob Willis

#### 48 TECHNICAL ABSTRACTS

#### DEPARTMENTS

- 8 AROUND THE WORLD

- 14 MARKET WATCH

- 45 OFF THE SHELF

- 47 MARKETPLACE

#### OCTOBER 2020 • VOL. 37 • NO. 10

# PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

# **FEATURES**

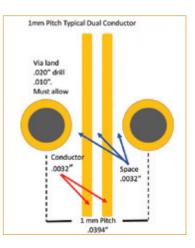

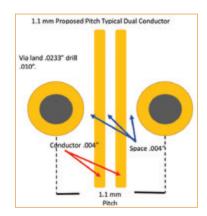

# 24 ROUTING *cover story*

#### The Case for a 1.1mm BGA/CGA Package

Because electronics engineers are forced to use a 1mm pitch package, we live with tradeoffs. A slight increase in the pitch size, however, could satisfy the needs for today's high I/O pin count designs.

by GERRY PARTIDA

#### 26 PRODUCT RAMP

#### 5 Things for Better Program Transfer from Prototype to Volume

Too many design projects go to waste or must restart from scratch because manufacturing at scale wasn't a building block of the development plan. Here are five things OEMs and EMS companies should do to better ensure a seamless transfer of programs from proto to volume.

by PAUL ROBERTSON, IAN HARDY and MATHIEU KURY

#### 30 PARTS VERIFICATION

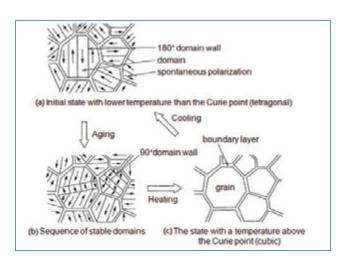

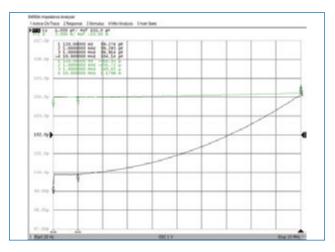

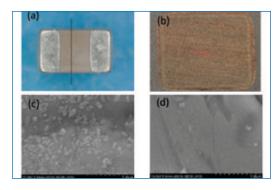

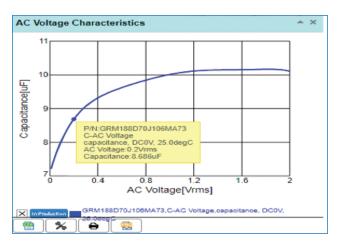

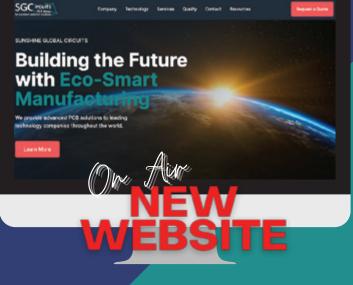

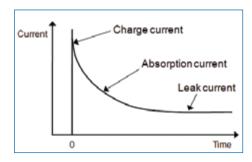

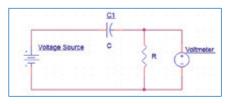

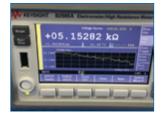

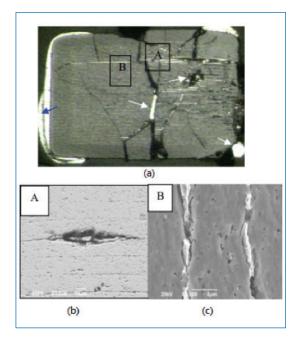

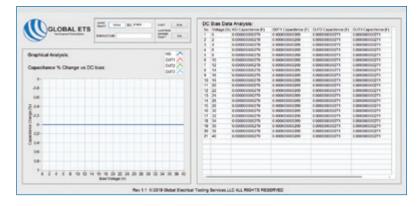

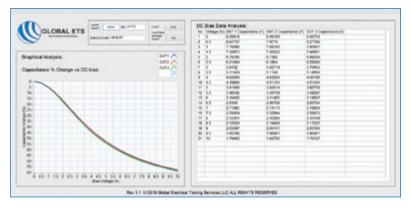

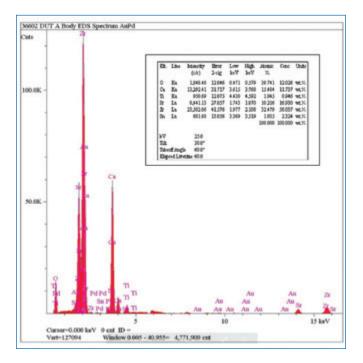

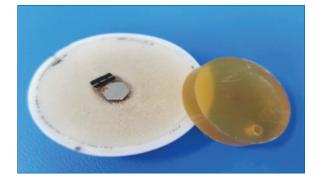

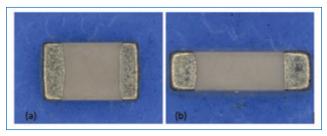

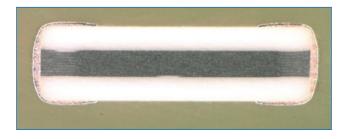

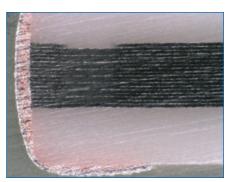

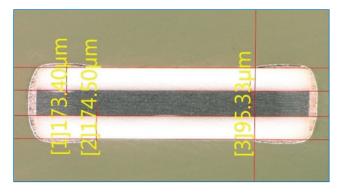

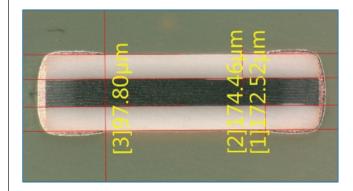

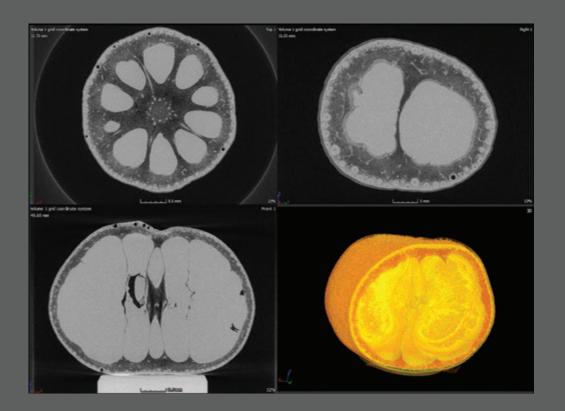

#### **Testing Method to Identify Counterfeit Multilayer Ceramic Capacitors** A study of test methods for MLCC compliance verification, including the effect of DC bias on capacitance, capacitance temperature characteristics, high-voltage testing of DCW (dielectric withstand voltage) and IR (insulation resistance), cross-section (dielectric layer and terminal comparison for flex types), and electron microscopy (EDS) material analysis to match with known good device chemical composition. by YUNG-HSIAO CHUNG, CHENG-HSUN LEE, LIWEI XU, YUQIAN HU,

ZONGXUAN WANG and STEPHEN E. SADDOW

# IN THE DIGITAL EDITION

#### The Digital Route What is the PCEA Educational Committee's role in education? by KELLY DACK

## The SMTAI Women's Leadership Program

Mentoring the next generation of engineers. Updates in silicon and electronics technology. by PRIYANKA DOBRIYAL

## ON PCB CHAT (pcbchat.com)

X-Ray Technology with BILL CARDOSO, PH.D.

Millennials in Manufacturing with MORIAH ROOT

Factory of the Future with MATT KELLY

The Charles Hutchins Award with ANDREW DAYA

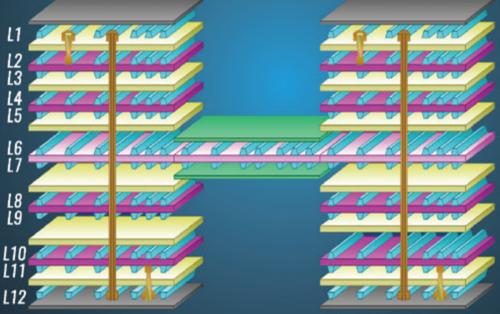

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

# When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

# Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

# Download our ebook on

# Signal Integrity For PCB Designers

- What is signal integrity?

- Need for signal integrity

- What leads to signal integrity issues in a PCB?

- o Impedance discontinuities

- o Reflections, ringing, overshoot and undershoot

- o Crosstalk

- o Via stub

- o Skew and jitter

- o Signal attenuation

- o Ground bounce

- o Power and ground distribution net

- o EMI noise

# DOWNLOAD NOW

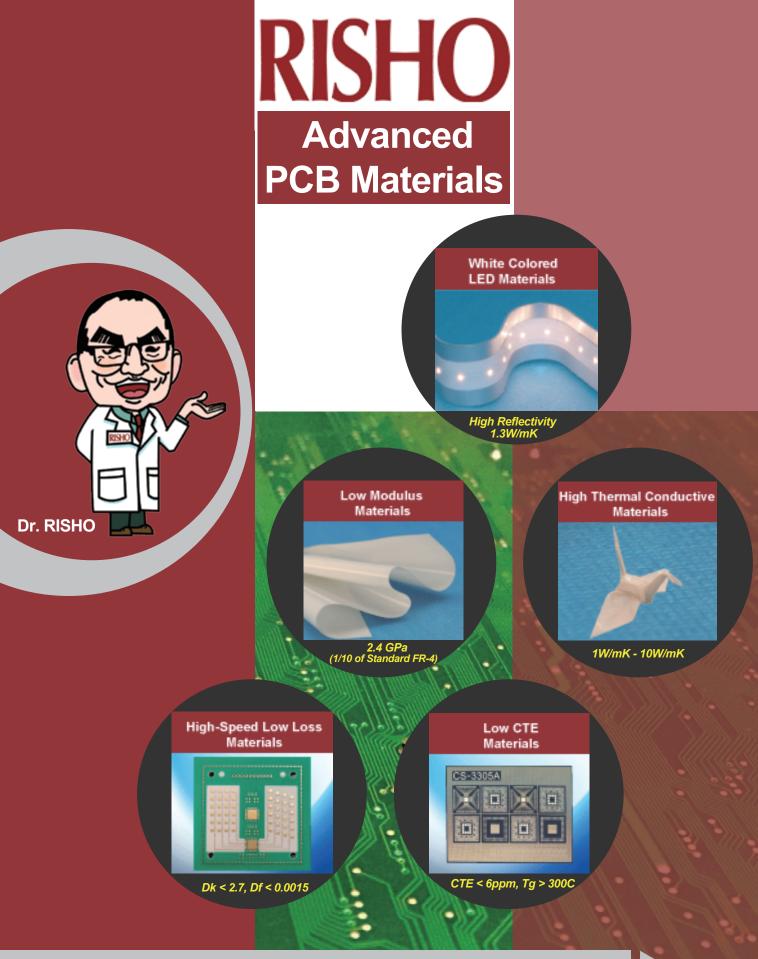

US Distributor: TechDream, Inc. www.tech-dream.com/pcb/risho/ 101 Bonaventura Dr. San Jose, CA 95134 (408) 829-3540 sales@tech-dream.com

# COMPREHENSIVE PCB DOCUMENTATION

#### Use 3D Models for Superior PCB Assembly Illustrations

Manage Layer Stackup Design and Materials

# BluePrint-PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings to drive fabrication.

of imported CAD data as a 3D PCB

Lowers documentation cost and time

Increases documentation detail & accuracy

Shortens PCB design cycles

Reduces documentation time by 60-80%

# downstreamtech.com • (508) 970-0670

©2020 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

# PRINTED CIRCL **DESIGN** & FA pcdandf.com

circuitsassembly.com

# **EDITORIAL**

EDITOR IN CHIEF Mike Buetow 617-327-4702 | mbuetow@upmediagroup.com

SENIOR EDITOR Chelsey Drysdale 949-295-3109 | cdrysdale@upmediagroup.com

DESIGN TECHNICAL EDITOR Pete Waddell

EDITORIAL OFFICE P.O. Box 470, Canton, GA 30169

#### PCD&F CONTRIBUTING EDITORS

Akber Roy, Peter Bigelow, John Burkhert, Mark Finstad, Bill Hargin, Nick Koop, Greg Papandrew

CIRCUITS ASSEMBLY CONTRIBUTING EDITORS AND ADVISORS Clive Ashmore, David Bernard, Robert Boguski, John D. Borneman, Joseph Fama, Susan Mucha, Chrys Shea, Jan Vardaman, Ranko Vujosevic

# PRODUCTION

ART DIRECTOR AND PRODUCTION blueprint4MARKETING, Inc. | production@upmediagroup.com

# SALES

SALES DIRECTOR Frances Stewart 678-817-1286 | fstewart@upmediagroup.com

SENIOR SALES ASSOCIATE Brooke Anglin 404-316-9018 | banglin@upmediagroup.com EXHIBIT SALES

Frances Stewart 678-817-1286 | fstewart@upmediagroup.com PRINT/FLECTRONIC REPRINTS

cdrysdale@upmediagroup.com

## SUBSCRIPTIONS

For changes, additions or cancellations: subscriptions@upmediagroup.com

# **UP MEDIA GROUP, INC.**

PRESIDENT Pete Waddell

VICE PRESIDENT. SALES AND MARKETING Frances Stewart

VICE PRESIDENT. EDITORIAL AND PRODUCTION Mike Buetov

DIRECTOR OF GROUP SHOWS

Alyson Corey acorey@upmediagroup.com

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. For others, annual Subscription Rates in U.S. funds are: \$80 (U.S. and Canada), \$145 (all other countries). Single copy price is \$8.50. All subscription and single copy orders or inquiries should be directed to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169, email subscriptions@upmediagroup.com. Photocopies and issues on Microfilm/Microfiche (16mm, 33mm or 105mm) are available from University Microfilms International, 300 N. Zeeb Rd., Ann Arbor, MI 48106, Telephone 313-761-4600.

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by UP Media Group Inc., PO Box 470 Canton, GA 30169. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

Periodicals postage paid at Canton/Ball Ground, GA, and additional mailing offices. © 2020, UP Media Group, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS Assembly is forbidden without written permission.

Postmaster: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169.

# Stuck in Stuck in the loop?

# First Time vs. Next Time

Deliver optimized designs the first time with **Valor® NPI**. By shifting manufacturing knowledge into the design process, concurrent DFM is now a reality, streamlining the design-to-manufacturing release process.

Design

Haudo Manufacturing

Respins

## CAVEAT LECTOR

MIKE BUETOW EDITOR-IN-CHIEF

# Fake Parts Still a Real Problem

**F THERE IS** one takeaway from the Symposium on Counterfeit Parts and Materials sponsored by SMTA and CALCE that took place in August, it is that the problem is getting worse. This should be alarming, given the amount of attention that has been paid to the presence of "fake" parts in the supply chain.

Discussion of counterfeits in the supply chain usually starts with the military. It's the one sector that has both the budget and the concentration of sourcing to effect change.

It was less than a decade ago that the US found fake electronic parts in military aircraft. The discovery spurred a yearlong investigation resulting in bipartisan legislation (remember what that is?) establishing new policies and practices for counterfeit avoidance.

Today, the annual US defense budget bills contain language requiring the Department of Defense, the Department of Homeland Security and their contractors monitor supply-chain risks for counterfeit parts, although previous language requiring buyers to "detect and avoid counterfeit parts in the military supply chain" has been softened.

Still, we've been battling the problem for at least two decades now, yet most experts feel 1) the volume of fake parts has increased, and 2) the counterfeiters are better than ever.

Methods for detecting fake parts over the years have included visual and optical inspection, XRF, chemical or laser etching, and even DNA marking. Our cover story this month centers on MLCCs, whose lack of markings and presentation, the authors note, "give unscrupulous vendors opportunities for fraud." The authors offer electrical (bias) testing, capacitance temperature characteristics, high voltage testing of dielectric withstand voltage and insulation resistance, and electron microscope (EDS) material analysis as possible nondestructive tests for separating authentic from fake.

The latest DoD proposals, submitted in August, focus on the Supplier Performance Risk System (SPRS), essentially an analytical tool for reviewing quality and delivery data from government systems. The proposed policy would tighten language above "item risk" to use SPRS to determine the probability that a product or service, based on intended use, will introduce counterfeit or nonconforming material to the DoD supply chain. In short, the Defense Department wants to continue down its path to basing supplier conformance on empirical data instead of subjective assessments.

There's nothing wrong with modeling risk; we do it all day long. But wouldn't a trusted supply chain, one inherently domestic, be a more predictable and authentic route? And does Covid-19 pose an opportunity? Most experts finger China (who else?) as the source for the vast majority (70% or more) of counterfeit electronics and related materials. Yet China remains the go-to for electronics materials.

Certainly, while the pandemic has brought about the most drastic global disruptions in memory to the supply chain, regional disruptions are commonplace. A new report from McKinsey Global Institute, the policy arm of the consulting agency, says there's inherent risk on so many depending on so few: "Interconnected supply chains and global flows of data, finance, and people offer more 'surface area' for risk to penetrate, and ripple effects can travel across these network structures rapidly." Their analysis of 37 industries ranks communications equipment as the one most exposed to value chain risks. Computers and electronics are seventh, and semiconductors are tenth. What these sectors' value chains have in common is their high value and relative concentration.

We are all aware how the supply chain became so concentrated in a single geography. The economies of scale only heighten the near-term costs involved in breaking China's grip on the electronics value chain. And it may be a stretch to overlay MGI's research into abrupt disruptions on a chronic pain point like counterfeits.

But the similarities are there. The presence of counterfeit parts is an ongoing disruption to an efficient chain. No one really knows how much is spent in mitigation and field returns, but all agree the figure is huge.

A McKinsey survey of supply chain executives conducted in May found some 93% plan to take steps to make their supply chains more resilient. Steps under consideration include building in redundancy across suppliers, nearshoring, reducing the number of unique parts, and supply chain regionalization.

If we are moving supply chains, we open the door to change. Western governments – and industries – should capitalize on the moment to beef up their local supply chains.

P.S. The PCB West Virtual 2020 technical conference is available on-demand through the middle of this month. Visit pcbwest.com for access.

# We're The Missing Link **To Your Supply Chain**

Fast Turn Domestic Capability | Cost Effective Offshore Capability **APCT: The Link To Your Success**

- Standard to Advanced HDI Technology

- Flex and Rigid Flex Technology

- Complete DFM Support

- Cycle Times Faster Than Industry Standards

- Defense & Aerospace Certifications

- Global Offshore Solutions Global Advantages Include:

- Ease of Use

- Seamless Recipe Transfer

- Inventory Management

- Risk Mitigation

# Contact APCT Today 408.727.6442 | APCT.com

# Printed Circuit Board Solutions

APCT.com

APCT Santa Clara HQ 408.727.6442

APCT Anaheim 714.921.0860

APCT Orange County 714.993.0270

APCT Wallingford 203.269.3311

**APCT Global** 203.284.1215

#### **PCDF** People

Cadence named **Patrick Davis** product manager director. He has nearly 25 years' experience as a PCB designer and manager with Rocket EMS, Summit Computer and Millennium Design.

# **PCDF Briefs**

Aotco Metal Finishing has acquired Plating for Electronics, a provider of specialty anodizing, electroplating, and laser marking services based in Waltham, MA.

All Flex has developed etched foil heaters for medical diagnostics, DNA testing, P.O.C. instruments and cancer diagnostics.

**Board Shark PCB** hired **ER North** as manufacturers' representative in North Dakota, South Dakota and Minnesota.

Sabic intends to boost production capacity for its proprietary resin to support growth of PCBs used in 5G base stations and highspeed servers.

Sanmina added RoBAT RCI backplane testing technology to its facilities in California and Mexico.

Schweizer Electronic named Varikorea sales representative for South Korea.

**Sumitomo Electric Industries** has succeeded in mass production of Fluorocuit, fluororesin-based flexible printed circuits for 5G applications.

Sun Chemical named Icaro to distribute its conductive and dielectric inks, as well as other electronic materials, in Mexico.

Taiwan-based PCB fabricators, now with 60% of their production capacity in China, are feeling more pressure to relocate their production plants to Taiwan, Southeast Asia and India.

**TPCA** is studying PCB factory smart manufacturing planning.

**Trackwise** installed a roll-to-roll direct imaging system and roll-to-roll flexible circuit laser drill.

**Unimicron Technology** sustained a fire at its PCB plant in Kunshan, China. The cause and extent of the damage are under investigation.

Ventec appointed Spectrum Marketing Associates sales representative for the US West Coast region and Mexico.

# IPC Task Group Edges Toward Finish of OSP Spec

**BANNOCKBURN, IL** – An IPC task group is making progress on a new standard for organic surface protectants for printed circuit boards.

The committee is developing a series of test methods to enhance the assessment of an OSP's ability to meet performance requirements of high-temperature soldering. The latest document is in draft form and should be ready for a membership vote by spring, the task group chairman said.

IPC-4555, Performance Specification for High Temperature Organic Solderability Preservatives (OSP) for Printed Boards, is a reboot of an effort begun more than a decade ago. In 2008, the task group attempted a similar standard, but was undone when a key OEM disputed the results of the solderability data. Unable to reach consensus, the task group disbanded the effort.

Last year, a new task group made up of major companies, including Continental, Bosch, Raytheon, TTM and Sanmina, embarked on a new draft. IPC tapped Michael Carano, vice president of technology and business development at RBP Chemical, to chair the task group.

OSPs are commonplace, which makes the lack of a performance standard notable. According to Carano, 62% of world's boards use OSPs. "They are in medical devices, tablets, airbags, engine controls, and telecom," he said, and used in combination with other final finishes in advanced packages.

The goal is to develop performance specifications for high-temperature OSPs, defined as capable of withstanding up to two IR reflows in conjunction with tinsilver-copper (SAC) or tin-bismuth (SnBi) alloys at a peak temperature of 245°-250°C and showing the same wetting balance results at three reflows as zero, with a maximum 20% drop.

The new spec calls for all classes of high-temperature OSP to have a minimum shelf-life of 12 months when left in original packaging and following recommendations of IPC-1601. Solderability must meet J-STD-003 category B. SIR will be measured per IPC-TM-650, Method 2.6.3.5, GR78-Core, and electrolytic corrosion per IPC-TM-650, Method 2.6.14.1.

Multiple round-robin studies were conducted to generate data to support the requirements in the pending specification, the task group said.

The issue that killed the spec a decade ago has been resolved. Back then, the task group could not agree on the allowable range of coating thickness. According to Carano, the current task group has agreed that coating thickness is not a determinant in the performance of the coating. "We don't need one big range," he said. Instead, the thickness requirement will be per the chemical supplier data sheet.

"OSP is difficult to test through the coating because the coating is hard, and, depending on the pin probe, you might bend the probe," Carano allowed. "Suppliers are working on ways around that."

"The thicknesses of most finishes can be measured with XRF. OSP uses a spectrophotometer. Or, we can verify the empirical data from a focused ion beam. The task group compared thickness with spectrophotometer with FIB cut, and they correlated very well. It's like accelerated corrosion testing."

For rework, the task group notes multiple methods exist for removing the immersion gold deposit to evaluate for the presence of hyper-corrosion of the nickel. Cognizant of the possibility of false positives for hyper-corrosion, the committee is working on the release of a specific test method to cover appropriate methods for gold stripping, which will be incorporated as an amendment upon release. (MB)

# Ucamco Releases Gerber Job Format Specification

**GENT, BELGIUM** – Ucamco released a Gerber job format specification that includes a schema that provides support for Gerber job format software developers.

The schema provides a definition of what can and cannot be inside a Gerber

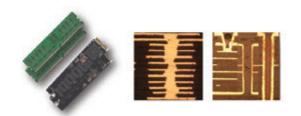

# Thin Lamination Board

TLB, a global leader in the 4th industrial revolution.

# **TRUST 2030**

Good Company in 20 Years, Great Company in 30 Years.

**TLB** is specialized in manufacturing PCB for semiconductors. By joining World Class 300 in 2018, we have become a company specializing in materials and components leading the fourth industrial revolution. Based on technology and quality, we will establish ourselves as a material parts company that leads not only Korea PCB but also world PCB.

# DRAM Module / SSD Module

# IOT / Build-up Board

# Semiconductor TEST B'd & 5G Network System

# TLB CO., LTD.

15602) 305, Sinwon-ro, Danwon-gu, Ansan-si, Gyeonggi-do, Republic of Korea Tel.82-31-8040-2096 Fax. 82-31-492-6623 Domestic Tel. 82-31-8040-2071, E-Mail. cmh@tlbpcb.com Offshore Tel. 82-31-8040-2060, E-Mail. will\_shin@tlbpcb.com

# CA People

pan Halder key account manager. He previously worked for NuEnergy.ai as an account executive, and also spent nearly three years in channel sales

at Honeywell.

Dan Oh, Ph.D., vice president of engineering of Samsung's Test & System Package (TSP) unit, will keynote the International Wafer-Level Packaging Conference and Expo in October.

Cogiscan appointed Sandi-

Enics named Mahmut Bertan chief business officer and Rami Aro director, services.

Indium promoted **Andy Mackie** to principal engineer and manager, thermal interface materials applications.

Inovar named Kent Johnson senior director of quality assurance. He has significant experience in defense, medical, aerospace, and nuclear power across a range of industries and a tech-

nical MBA from the University of Utah.

Intervala named Eric Sicard senior business development manager. He spent the past seven years at TT Electronics, most recently as market development manager, and was

previously vice president of supply chain for API Defense and director of sourcing for OnCore Manufacturing.

Knowles Precision Devices named **Brook Sandy** applications engineer, RF and Microwave. She previously was technical conference program manager at IPC and spent 11

years in engineering support at Indium and Henkel.

Meridian Adhesives Group appointed Brandon Willis president of the company's Electronics division.

Nortech Systems CFO **Connie Beck** resigned to pursue an executive position at a private company. Corporate controller **Alan Nordstrom** will serve as acting CFO.

Part Analytics appointed Jim Robinson head of sales, responsible for all new OEM sales and support initiatives in the US. Most recently, he was chief commercial officer for

Sleek Fleet, and held management positions at Microsoft and Google.

job file. It can be used programmatically to check a Gerber job file for errors and is mainly intended for reading or writing Gerber job files.

Any JSON schema reader that can parse a draft-07 schema can be used to read it and check Gerber job files against it for errors. (CD)

# **US PTO Publishes Apple Patent Application** on Smart Fabrics

**CUPERTINO, CA** – The US Patent and Trademark Office published a patent application from Apple that discusses the manufacture of smart fabrics with specialized equipment that could be used to form fabric with integrated electrical components, according to reports.

Apple's patent application notes it may be beneficial to incorporate electrical components into fabric, but since fabric is flexible, new techniques are required. The company's invention covers interlacing equipment: for example, weaving equipment, knitting equipment, and braiding equipment.

Woven fabric may include insulating and conductive material, and conductive strands may form signal paths through fabric, coupled to electrical components such as light-emitting diodes and other light-emitting devices, ICs, sensors, and haptic output devices.

End products for next-generation fabric intertwined with electronics could relate to smartphones, computers, or other portable electronic devices, Apple says in the application.

Apple's patent application was filed in March, but some of the original work dates to 2019. (CD)

# East West Goes North, Buys Universal Electronics

**ATLANTA** – East West Manufacturing in September announced the acquisition of Universal Electronics in a deal between privately held contract electronics manufacturers. Terms were not disclosed.

Whitewater, WI-based Universal Electronics builds printed circuit board assemblies, box-build assemblies, and performs testing and new product introduction. It was founded in 1980. It has nine SMT lines across its 87,000 sq. ft. plant in Whitewater and 40,000 sq. ft. plant in East Troy. It has estimated sales of more than \$60 million, according to the CIRCUITS ASSEMBLY Directory of EMS Companies.

UEI advances East West's strategic focus on growing its domestic electronics manufacturing capabilities and expanding its US manufacturing operations, the company said in a press release. The acquisition extends East West's geographical reach in the Midwest, where the site is close to many current customers.

The purchase of UEI continues an acquisition plan by East West that includes prior buys of Team Manufacturing in 2018 and General Microcircuits and Adcotron in 2019.

"We are excited to partner with UEI to expand our manufacturing operations to the Midwest," said Scott Ellyson, cofounder and CEO, East West. "UEI has an incredible reputation for putting its customers first and has an established presence in a variety of high-growth sectors such as medical, industrial, telecommunications and defense. This acquisition allows us to offer greater domestic, higher mix, lower volume, quickturn electronic manufacturing services. Our collective design, manufacturing and supply chain capabilities will enable us to provide even greater levels of service and support to customers on a global basis."

"The leadership team and associates here at UEI are excited about becoming part of the East West family. Our culture, capabilities and customer-first focus align perfectly," said Rick Jensen, owner and president, UEI. "We expect the new combined company to help our customers continue to grow." (MB)

# The Circuits Assembly Directory of EMS Companies

- Build your EMS database

- 3,000+ facilities worldwide

- Sortable in Excel

- Unrestricted use

- Includes contact info, no. of lines, markets served and more!

circuitsassembly.com/dems

SVI Public Co. named Angkana Sornsakarin chief accountant.

Tempo Automation named **Ryan Benton** chief financial officer. He has nearly 30 years of financial, operational and strategic experience, most recently as CFO of Revasum,

a publicly listed semiconductor capital equipment company.

# **CA Briefs**

**Apple** is expected to see a sharp rise in purchases of server components in 2020 and 2021 due to expansion of internal datacenters.

AQS purchased a **Precision PCB Services** SV500 BGA rework system.

**Board Shark PCB** named **MarTec** to provide sales and service in Alabama, Georgia, Mississippi, and Tennessee.

**CalcuQuote** and **Advanced Assembly** announced a new collaboration to expand software functionality and streamline processes through digital innovation.

**Compaq** and **Ossify Industries** have launched a range of QLED TVs in India.

**Computrol** purchased a **Viscom** X7056-II 3-D x-ray inspection system and an **Aqueous Technologies** Trident LDO-DUO cleaning system.

**Dorigo Systems** is showing off its new 105,000 sq. ft. EMS plant in Burnaby, BC.

**Foxconn** and **Pegatron** are reportedly eyeing new factories in Mexico as the US-China trade war and coronavirus pandemic take their toll on global supply chains.

Foxconn's chairman told investors China's "days as the world's factory are over."

An Indian panel has approved a plan by **Foxconn, Pegatron, Wistron** and others to export mobile phones worth around \$100 billion, or Rs 7.3 lakh crore, from India.

Some 15 tonnes of copper scrap were reportedly stolen from **GPV's** facility in Tarm, Denmark, the second break-in since July.

Jabil has selected Keysight's 5G device test solutions to address the demand for 5G product validation in design and manufacturing. Jabil is also suing Singer, saying it was not reimbursed for more than \$2.6 million in pre-production costs.

Nortech Systems has completed the sale and leaseback transactions for its manufacturing facilities in Bemidji and Manka-

# Creation Technologies Breaks Ground on EMS Plant in Hermosillo

**HERMOSILLO, MEXICO** – Creation Technologies has broken ground on a high-volume electronics manufacturing facility here that will nearly triple its Mexico footprint. The company is expanding its North American footprint to better serve aerospace and defense, medical, and tech industrial customers.

The new facility will provide more capacity, with a total of 205,000 sq. ft., bringing total capacity of Mexico operations to 330,000 sq. ft., including existing capabilities in Mexicali. It is scheduled to be operational in the third quarter of 2021.

"We are thrilled to announce our plans for a significant expansion of our manufacturing capacity in Mexico," said Stephen P. DeFalco, chairman and CEO, Creation Technologies. "This expansion builds on our current Mexico operations, where we have over 700 dedicated employees focused on providing outstanding service to our customers' high-reliability needs."

The site will have space for up to 12 automated SMT lines and will be a purposebuilt greenfield facility designed for Lean factory flow.

The facility will provide dedicated areas for PCB assembly, system integration and test, as well as forward and reverse logistics. (MB)

# Gowanda REM-tronics to Close EMS Plant in NY

**DUNKIRK, NY –** EMS firm Gowanda REM-tronics will shutter its plant here Nov. 15, eliminating 69 jobs, according to reports.

Staff received a letter stating Gowanda Components Group and its affiliates have been "adversely affected" by economic factors. The company said trouble in the avionics and fiberoptic sensor markets led to the "shutdown of entire industries," affecting orders.

The factory supplies to the aerospace, industrial, medical and military industries. (CD)

to, MN, at a sale price of \$6.3 million. It also will close a production plant in Merrifield, MN, affecting 60 to 70 jobs.

**Outroar LLC** has launched new EMS PCB assembly services under the name **Titan Circuits**.

**Specialty Coating Systems** moved its Parylene coating center to a new 6,000 sq. ft. multipurpose facility in Dublin.

**TopLine** announces the availability of comprehensive FPGA repair, rework, and column attachment services.

The University of Wisconsin-Madison has received less than 1% of the money Foxconn pledged to it two years ago. In August 2018, Foxconn committed \$100 million to the university to help fund an engineering building and for company-related research.

The **US Defense Department** is proposing to amend the Defense Federal Acquisition Regulation Supplement (DFARS) to update the policy and procedures for use of the Supplier Performance Risk System.

The US Undersecretary of Defense for Acquisition and Sustainment says America can "no longer clearly identify the pedigree of our microelectronics. Therefore, we can no longer ensure that backdoors, malicious code or data exfiltration commands aren't embedded in our code."

Violet Defense has awarded SMTC a multimillion-dollar, multiyear contract to build Xenon UV disinfection devices.

**Virtex** announced the creation of 40 to 50 new manufacturing jobs at its EMS plant in Waynesboro, VA.

Viscom sold S3016 ultra 3-D AOI to Bosch and E.D.&A.

Weller Tools named Cardinal Marketing manufacturers' representative in Illinois and Wisconsin.

# Understanding High-Speed onstral

FREE new e-book!

pcdandf.com/pcdesign/constraints

This fabulous treatise allows PCB designers and engineers to understand all the important constraints and determine their values.

SECOND

details on edge rates;

graphics & equations; references on via impedance

written by Charles Pfeil

Charles Pfeil has spent over 50 years in the PCB industry as a designer, owner of a service bureau, and in engineering management and product definition roles at Racal-Redac, ASI, Cadence, PADS, VeriBest, Mentor Graphics, and Altium. He was the original product architect of Expedition PCB.

| TVS TURNED ON                                                                                                                                                      |      |               |      |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|-------|

| Trends in the U.S. electronics<br>equipment market (shipments only).                                                                                               | MAY  | % CHA<br>Jun. |      | YTD%  |

| Computers and electronics products                                                                                                                                 | 0.3  | -0.3          | 4.0  | 1.5   |

| Computers                                                                                                                                                          | 2.1  | 0.2           | -3.0 | -11.3 |

| Storage devices                                                                                                                                                    | -2.1 | -4.9          | 1.6  | 46.6  |

| Other peripheral equipment                                                                                                                                         | 9.5  | -14.5         | 20.3 | 6.3   |

| Nondefense communications equipment                                                                                                                                | 0.2  | -0.4          | 9.5  | 7.2   |

| Defense communications equipment                                                                                                                                   | 7.2  | 1.1           | -4.5 | 0.4   |

| A/V equipment                                                                                                                                                      | 4.0  | 13.9          | 11.0 | -13.9 |

| Components <sup>1</sup>                                                                                                                                            | -0.3 | 0.0           | 5.5  | 9.1   |

| Nondefense search and navigation equipment                                                                                                                         | -0.7 | 1.0           | 1.4  | -6.4  |

| Defense search and navigation equipment                                                                                                                            | -0.2 | 0.2           | 2.2  | 3.0   |

| Medical, measurement and control                                                                                                                                   | 0.0  | 0.2           | 0.4  | -3.5  |

| <sup>1</sup> Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjusted.<br>Source: U.S. Department of Commerce Census Bureau, Sept. 2, 2020 |      |               |      |       |

# Hot Takes

- Personal computing devices, including traditional PCs, tablets, and workstations, will grow 3.3% year-over-year in 2020, with shipment volumes reaching 425.7 million units. (IDC)

- By 2030, augmented, virtual and mixed reality optics and display markets are expected to total more than \$28 billion. (IDTechEx)

- Total smartphone production reached 286 million units in the second quarter, a sequential rebound of 2.2% but a 17% drop year-over-year. (TrendForce)

- The worldwide smartphone market is forecast to decline 9.5% year-over-year in 2020, with shipments totaling 1.2 billion units. (IDC)

- The consumer electronics market is expected to surpass \$1.5 trillion by 2026, up from \$1 trillion last year. (Global Market Insights)

- The output of PCBs in Japan in June was down 234% yearover-year to 803,000 sq. m. (JPCA)

- Global home audio posted second quarter shipment growth of 20% sequentially. (Futuresource Consulting)

- The fan-out wafer level package (FO-WLP) market is projected to grow 15.5% in units from 2020 to 2024. (Tech-Search International)

- The worldwide electronics assembly market consisted of approximately \$1.3 trillion in terms of cost of goods sold as of 2019. (New Venture Research)

- M&A activity in the EMS sector stalled in the second quarter, with just three deals closing in the period. The three deals included two consolidations and one vertical/horizontal convergence. (Lincoln International)

- Taiwan automotive PCB shipments declined 6.7% in the first half, the only segment with negative sales growth in the domestic industry. (TPCA)

- The overall 5G enterprise market will reach \$2.3 billion in 2020 and is projected to reach \$31.7 billion by 2026, at a CAGR of 54%. (MarketsandMarkets)

- The printed electronics market is forecast to grow 4% from 2020 to 2026. (ReportLinker)

| US MANUFACTURING INDICES                               |      |      |      |      |      |

|--------------------------------------------------------|------|------|------|------|------|

|                                                        | APR. | MAY  | JUN. | JUL. | AUG. |

| PMI                                                    | 41.5 | 43.1 | 52.6 | 54.2 | 56.0 |

| New orders                                             | 27.1 | 31.8 | 56.4 | 61.5 | 67.6 |

| Production                                             | 27.5 | 33.2 | 57.3 | 62.1 | 63.3 |

| Inventories                                            | 49.7 | 50.4 | 50.5 | 47.0 | 44.4 |

| Customer inventories                                   | 48.8 | 46.2 | 44.6 | 41.6 | 38.1 |

| Backlogs                                               | 37.8 | 38.2 | 45.3 | 51.8 | 54.6 |

| Source: Institute for Supply Management, Sept. 1, 2020 |      |      |      |      |      |

| KEY COMPONENTS                                                                                                                                                             |       |       |       |                    |                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------|---------------------------|

|                                                                                                                                                                            | MAR.  | APR.  | MAY   | JUN.               | JUL.                      |

| Semiconductor equipment billings <sup>1</sup>                                                                                                                              | 21.2% | 18.7% | 13.5% | 14.4% <sup>r</sup> | 27.6% <sup>p</sup>        |

| Semiconductors <sup>2</sup>                                                                                                                                                | 6.85% | 6.13% | 4.82% | <b>4.95%</b> r     | <b>4.92%</b> <sup>p</sup> |

| PCBs <sup>3</sup> (North America)                                                                                                                                          | 1.15  | 1.19  | 1.10  | 1.12               | 1.00                      |

| Computers/electronic products <sup>4</sup>                                                                                                                                 | 5.43  | 5.44  | 5.44  | 5.44 <sup>r</sup>  | 5.28 <sup>p</sup>         |

| Sources: <sup>1</sup> SEMI, <sup>2</sup> SIA (3-month moving average growth), <sup>3</sup> IPC, <sup>4</sup> Census Bureau, <sup>p</sup> preliminary, <sup>r</sup> revised |       |       |       |                    |                           |

We realize ideas

# High-Quality PCB Connection Technology

- > Spring Clamp and Screw Type Terminal Blocks

- > Board-to-Board Connectors

- > RJ45 & M12 Jacks and Plugs

# Meeting of Minds: Are Company Events 'Virtually' Never-ending?

As communication shifts online, time management becomes a group effort.

TIME MANAGEMENT, THE operative word being *management*, is never easy to master. Scores of books and lectures elaborate on how to stop the interruptions, focus on the important, and liberate one's ability to get things done. Even so, the challenge has become even more elusive over the past year.

Until recently, time management focused on how to reduce interruptions from various activities and events, such as unwanted phone calls, perpetual cubicle chats, and the length and focus of conference room meetings. Historically, those were leading contributors to inefficiency and wasted time. That was then; this is now.

Communication has become email-centric. Phone tag is no longer the corporate sport. A typical workday commences by sorting the email inbox, vetting the important ones, and then doing the same in the spam folder filled with six zillion missives, many from finance ministers of countries no one has ever heard of. Face-to-face interaction, however, has remained tied to the corporate conference room, where at any time different combinations of coworkers, customers and suppliers meet to solve some problem or communicate about new or changing opportunities.

Over the past year a seismic shift has taken place. Social distancing, travel restrictions and workfrom-home have altered the workplace and how we collaborate. Tools that were known but not generally deployed – like Zoom and WebEx – are now the preferred methods of group communication and collaboration. As convenient and spontaneous as these technologies are, they have wreaked havoc on time management as we know it.

Efficient use of time typically means arranging events, such as meetings and customer/supplier visits, into time blocks around which other activities can be scheduled. The sales staff visits several customers in a similar location on a single trip. Ditto the purchasing staff when visiting suppliers. Company meetings are set for a time and date when all participants are in the office. And most of all, because of logistics such as travel time, they spread out to keep those costs to a manageable minimum. Time was managed in advance based on schedules. Effective time management successfully eliminated the sporadic interruptions that torpedoed otherwise well-planned days.

The current work environment has changed dramatically. Employees rarely work in the office. Customer and supplier visits are increasingly virtual. Schedules are flexible. Spontaneous virtual meetings, gatherings and collaboration, often outside the traditional "9 to 5" business hours, have become the norm. And because technology permits it, "regular" meetings seem to be more frequent and include a far greater number of participants. All this tanks traditional time management strategies.

Successful time management is now as much a group effort as an individual initiative. Good time management still includes sharing a schedule with colleagues, communicating it through whatever method – usually electronic – your organization utilizes. It still requires focus on what is important. However, it is more important than ever for the organizer of a virtual meeting, gathering or event to plan!

Think beyond just the purpose of the virtual gathering. Other planning is critical to manage time effectively. Ask: How long is reasonable for the meeting to last? Who must attend vs. who may want to be included? Most important, how frequently will the virtual event be held? This last point may be the single contributor to inefficient time management.

Do you find monthly meetings become weekly meetings, and one-off gatherings morph into ongoing scheduled events? Just because we *can* meet doesn't mean we *must* meet. Spontaneity can be great, and with coworkers and colleagues seemingly so flexible and available, virtual meetings are easy. But when they become too frequent or spontaneous, they tend to accomplish less, and the time consumed outweighs the benefits. The virtual event itself overshadows the reason the event was needed in the first place.

Right up there with meeting frequency is being clear as to who needs to vs. who could attend. Again, discerning *need* vs. *could* is critical to effective time management. The more people involved, the more time each virtual meeting inevitably takes. Compounding this basic time management inefficiency is the number of nonessential people who instead need the time to accomplish more important tasks. Most virtual meetings or events are arranged to accomplish a specific result, so it is critical to keep the attendee list to just those who are needed. Be proactive. The organizer should identify which participants are necessary and which participants are welcome only if more important activities aren't on their plate.

Finally, everyone needs to stick to the schedule. If the event is scheduled to take one hour, do everything possible to keep to that time. If it looks like the subject needs five more minutes to complete, offer that as an option before scheduling the next meeting. Regardless of technologies utilized, locations of employees and colleagues, or the purpose of the meeting, effective time management means a shared focus on getting things done. PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

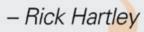

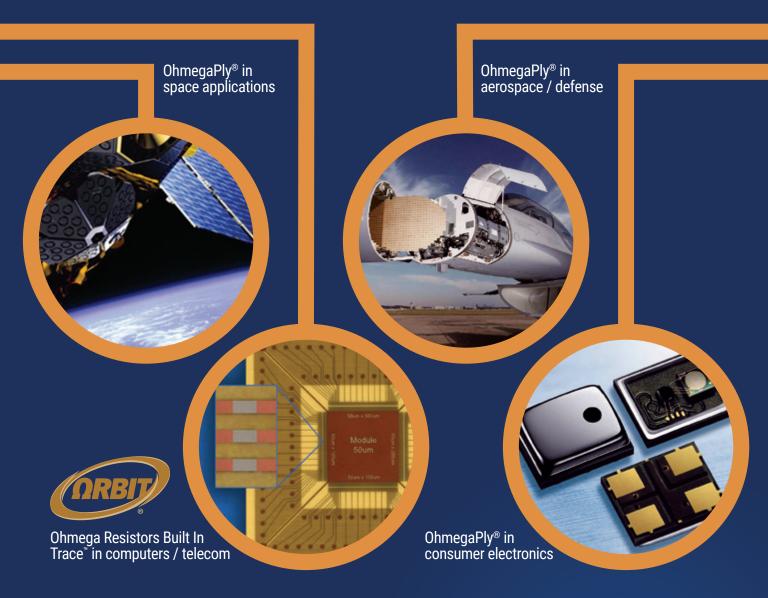

# **Proactive innovation. That's been the Ohmega hallmark for five decades.**

Over that time, we have been proactive in meeting the constantly changing and demanding requirements of the design engineer. Our focus on innovation, product improvement and enhancements has kept OhmegaPly<sup>®</sup> as the benchmark for embedded resistive materials. On land, in the sea, in the air, and in space, when your mission is critical, you need Ohmega onboard.

YOU NEED OHMEGA ONBOARD

310.559.4400 • www.ohmega.com

# Hindsight is '2020': The Organizational Stress Test

The big lesson from this unpredictable year is infrastructure planning pays.

"HINDSIGHT IS 20:20" refers to a vision measurement, not this crazy year. But from a planning standpoint, the year "2020" has rewarded electronics manufacturing services (EMS) companies that built resilience into their operational plans. As I write this, the Covid-19 pandemic continues to spur an era of new normal. The introduction of vaccines will hopefully drive a return to something close to the old normal. While this challenge is ongoing, however, it is important to look at some of the operational investments that have proved most beneficial.

Here are five areas that stand out to me:

**IT.** Companies that were already supporting employees working remotely as a result of business travel, remote home offices or a need to work in multiple time zones more comfortably had an edge in converting a larger portion of the workforce to work-at-home scenarios. VPNs, internal systems capable of supporting secure and fast access to remote users, videoconferencing tools, seamless transfer of work phones to mobile phones, and existing policies/training on maintaining security in home office environments are all key elements enabling employees to effectively work at home. Companies with these in place simply had to scale up to accommodate a larger user base. Systems strategy has also been integral in managing the supply chain and forecasting disruption driven by Covid-19. Companies with systems that can quickly assess inventory levels, material availability and production status globally were better off than those with facility-specific systems or systems that required much manual interpretation to gather that information.

Issues to consider in future investments include:

- What security vulnerabilities did work-at-home scenarios create, and how does the protection and training strategy need to change?

- Were connections fast enough for remote work and communication?

- Overall, are systems providing enough status visibility when forecasts, availability and production capacity/output are changing rapidly?

Design for procurement. Covid-19 hit just as industry was returning to normal from multiple years of supply-chain constraints. Companies with good discipline in terms of getting customers to specify or approve alternates on all component line items, internal stocking programs, and good relationships with a broad base of suppliers were better prepared for Covid-19 disruptions. Unlike the previous constraints, Covid-19 disruptions ran the gamut: closed factories, logistics surprises and prioritized demand under the Defense Production Act. Consequently, it wasn't a matter of getting in line for a later delivery on an allocated part. In some cases, it required a quick switch to alternate suppliers or broker authorizations because there was no clear timeline on when the original part would be available. There was also little predictability on which suppliers would be disrupted because factory closures and shipping disruptions were occurring all over the world. Internal stocking programs and finished goods kanbans helped buy time when alternate arrangements were needed, but they weren't a total solution.

Issues to evaluate include:

- Is the purchasing department too dependent on a limited supply chain?

- Do program managers help customers scrub BoMs and AMLs early to flag potential part problems and ensure options are identified and approved for most of the BoM?

- Are stocking programs and finished goods kanbans sized appropriately?

- Do any areas of the supply-chain disruption mitigation strategy need to be enhanced?

Rapid, repeatable NPI. New product introduction has a lot of definitions in the EMS industry. In some companies it is a unique process every time, predominantly driven by customer requirements. In other companies there is a formal base process with a defined timeline, support team and systems which support rapid transfer and verification of documentation, process validation and initial builds. Companies with well-defined processes were in a better position to add business from companies needing to reshore or expand their suppliers to deal with disruptions or excess demand in their existing supply chain.

Issues to evaluate include:

- Were any opportunities lost because of an inability to launch a new project quickly enough?

- Are the systems supporting the NPI process automated enough to support rapid response?

- Is the NPI process well defined and repeatable enough to launch projects rapidly without mistakes?

Lean manufacturing. Lean manufacturing philosophy offers a variety of benefits, including scheduling flexibility, optimized throughput and better organized factory floors. All these things have come into play during the pandemic. Some OEMs increased orders dramatically in medical or critical infrastructure sectors. Others cut forecasts or ceased production, then began increasing orders to address pent-up demand later in the

president of Powell-Mucha Consulting Inc. (powellmuchaconsulting. com), a consulting firm providing strategic planning, training and market positioning support to EMS companies and author of Find It. Book It. Grow It. A Robust Process for Account Acquisition in Electronics Manufacturing Services: smucha@powellmuchaconsulting com.

**SUSAN MUCHA** is

# Panasonic

Ultra-low Transmission Loss Multi-layer Circuit Board Materials for ICT Infrastructure Equipment

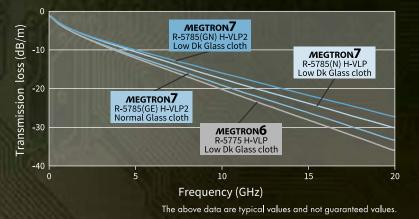

# MEGTRON (G)type NEW Laminate R-5785(GN), R-5785(GE)

Prepreg R-5680(GN), R-5680(GE) (GN):Low Dk Glass cloth type (GE):Normal Glass cloth type

# Features

- Improved lamination processability compare to MEGTRON7 R-5785(N)

- Glass transition temperature (Tg): 200°C (DSC)

- Multi-site production in Japan/China

|            | Dk  | Df               |

|------------|-----|------------------|

| R-5785(GN) | 3.4 | 0.002<br>@ 12GHz |

| R-5785(GE) | 3.6 | 0.003<br>@ 12GHz |

# Applications

• High-end servers, High-end routers, Supercomputers, and other ICT infrastructure equipment, Antenna (Base station, Automotive millimeter-wave radar), etc.

# Transmission Loss

Construction

| t h                     |                       |  |  |

|-------------------------|-----------------------|--|--|

| Trace thickness(t)      | 18µm                  |  |  |

| Dielectric thickness(h) | 300µm                 |  |  |

| Copper thickness        | 18µm                  |  |  |

| Inner treatment         | No-surface treatment  |  |  |

| Core                    | 0.15mm (#1078 x 2ply) |  |  |

| Prepreg                 | 0.15mm (#1078 x 2ply) |  |  |

| Line length             | 1000mm                |  |  |

| Impedance               | 50Ω                   |  |  |

DISTRIBUTOR IN NORTH AMERICA MATRIX USA INC. TORONTO • SANTA ANA • SANTA CLARA • CHICAGO • MINNESOTA Visit our website at www.matrixusa.us

Contact us

Partnering to go beyond.

#### Electronic Materials Panasonic Corporation

NTRODUCING

AIM Tech Tutorials

a new how-to video series featuring

the AIM Technical Experts. Watch on

www.aimsolder.com/videos today!

year. Some EMS factories needed to shut down or had capacity constraints due to local mandates on employee headcount. Companies with production processes optimized for scheduling flexibility, combined with good visibility into inventory, material on order and production status, were in the best position to address this chaos. Additionally, the level of organization and lack of clutter or work-in-process (WIP) found in most facilities focused on Lean manufacturing principles made it easier to address mandated social distancing requirements.

Issues to evaluate include:

- Did equipment constraints create bottlenecks or otherwise limit flexibility in accommodating demand increases?

- Did factory clutter or WIP create issues in implementing recommended social distancing practices?

- Is the company too Lean in areas such as inventory to accommodate this level of disruption?

- Is there sufficient commonality in equipment and processes among facilities to accommodate rapid transfer of work in the event of facility shutdowns?

**Cross training.** Cross training makes it easier to shift employees around a factory as demand changes. It also makes it easier to accommodate vacations or absences. Companies that had invested in cross training were able to give production workers more flexibility in shift choices as schools closed and childcare became a problem. They also have been better situated to cope with attrition or headcount constraints driven by employee health concerns or local restrictions.

Issues to evaluate include:

- Were all employees who needed shift changes due to personal issues accommodated?

- Were there surprises in the employee competencies when workers changed shifts that should be better addressed in future training programs?

- Have enough employees been crosstrained in critical functions to accommodate absenteeism where sick employees are asked to stay home and employees with health issues may want to stay home?

- Does current shift structure fit the needs of the labor market, or would a different schedule better accommodate the workforce?

None of these five areas of investment is groundbreaking or new. Many companies are investing in these areas at some level. While 2020 is a year no one is likely to want to repeat, the organizational stress test is invaluable. In a year where all the original plans were wrong, investments made in these areas turned out to be of far greater value than anyone likely assumed. Companies that take the time to evaluate the gaps in infrastructure identified in this reactionary environment and the organizational investments that outperformed expectations, and incorporate that knowledge in their future planning, will likely leave 2020 in a better position than they entered it.  $\Box$

AIM's worldwide technical support network of IPC certified engineers assists customers in obtaining optimal results in local time and local language.

AIM's commitment to ongoing research and development enables the company to develop innovative solutions for the manufacturing challenges of tomorrow.

AIM facilities are IATF 16949 and ISO 14001/9001 certified, ensuring sustainable, reproducible results around the globe.

# AIM Global Solder Solutions

www.aimsolder.com | info@aimsolder.com

# Made in America is Great – If You Can Do It

American manufacturers are throwing away business opportunities. Are you?

ACCORDING TO A recent statement by US Undersecretary of Defense for Acquisition and Sustainment Ellen Lord, national electronics procurement is at a crossroads.

"[America] can no longer clearly identify the pedigree of its microelectronics," she said. "Therefore, we can no longer ensure that backdoors, malicious code, or data exfiltration commands aren't embedded in our code."

According to Lord, a variety of price pressures – ranging from government regulations to labor costs – have driven manufacturing of electronics offshore and created not only an economic imbalance but a security threat as well. "That's what we need to reverse," she said.

Like the Defense Department, American consumers also support bringing manufacturing back onshore. They believe the "Made in USA" slogan means saving American jobs and, often, superior quality of goods. They support "reshoring" – bringing the manufacturing and assembly of goods – back to the US.

But would that actually work? Would US PCB customers receive the same service from domestic sources they get from offshore assembly houses and manufacturers? Can domestic PCB suppliers keep up with demand and provide timely delivery?

The answer, unfortunately, is no, unless domestic firms make some critical changes.

Since the onslaught of tariffs and the Covid-19 pandemic, my firm has received many inquiries for new projects to be fabricated or assembled domestically, along with possibly reshoring ongoing work. It's a noble intention, and we've been trying to help. We've reached out to more than a dozen North American PCB assembly houses and manufacturers to get work placed.

The experience has been a mixed bag, to say the least. Here is what we have encountered in our search for domestic shops:

Inflexible order sizes. Domestic companies with huge assembly operations seek large-volume orders and won't quote a job less than about \$2 million annually in revenue. On the other hand, most domestic fabricators prefer small to midrange run orders. They won't take on customers with the mid-to-higher-volume business typically made offshore. Plenty of customers with orders in that range couldn't place their business domestically even if they wanted to. That's a shame. Offshore companies are aggressively quoting NPI programs. If China can compete on small lots, then the US should at least try to compete on big ones.

Inefficient quoting. I can't tell you how many times after I have submitted an RFQ that I have to either follow up to confirm the RFQ receipt, or call weeks later looking for an update on the quote. And the US-based sales department frequently fails to communicate pertinent information to its quoting team, so the quote is inaccurate. Or a quote has been sitting overlooked on someone's desk or in their email. I get better communication from companies on the other side of the world.

Every assembly quote is different, each with its challenges. But like most processes in our industry, quoting should follow established procedures. What is your company's policy for quote response time? (Do you have one?) How often do you hit your target? And when the promised response date has passed, do you always call the customer to notify them of the reason for the delay?

- Refusal to quote. One shop I tried to get quotes from – a new state-of-the-art facility that touts its production capability – flat-out refused because they "don't want to compete with China." I explained the end-customer understands the price would be higher and still wanted a quote. The answer remained "no." What's going on here?

- Poor customer service. Do you have problems with simple stuff, like getting people to respond to an email or return a call in a timely manner? Me too. There's also a lack of urgency with the basics, like notifying customers about schedule changes or ensuring paperwork is correct.

These are companies I've done business with before. In many cases, I personally know the owner. They know I have many customer contacts. If they treat me this way, how do they treat an unknown prospect?

Unwillingness to invest in technology. Because of customer requests, I've been trying to reshore existing volume orders, with some difficulty. One of my domestic board shop connections is an established facility known for large-volume orders.

# GREG

PAPANDREW has more than 25 years' experience selling PCBs directly for various fabricators and as founder of a leading distributor. He is cofounder of Better Board Buying; greg@ boardbuying.com.

Unfortunately, this company appears averse to change, especially when it comes to upgrading the equipment needed for today's technology that would permit it to compete globally.

Investing in capital equipment isn't cheap, but it is certainly more costly to our industry when domestic shops fail to meet the rising technology curve and cannot fulfill customer demands. Perhaps a collective could be formed to improve capital expenditure purchasing terms and,

since hardly any PCB equipment is manufactured in the US, ensure a domestic ample inventory of spare parts. Investment in local personnel who could provide tech support for the equipment is also advisable.

When an OEM approaches me for help, I recommend a domestic source about 80% of the time. I've found that when a domestic supplier goes headto-head with an overseas manufacturer – factoring in tariffs, minimum order values, overseas delivery, and time-zone delays – the total cost of ownership (TCO) for PCB assembly is comparable in the US to offshore.

(Many customers forget tariffs add to the bottom line. While 2- and 4-layer bare boards are exempt, 2and 4-layer *assemblies* are subject to tariffs.)

Thus, it is even more frustrating when domestic assemblers refuse to accept quotes or fail to deliver decent service. The TCO often favors a domestic manufacturer – *if* an OEM can find one willing to build mid-tohigher volumes. American manufacturers are throwing away business opportunities.

Of course, many domestic PCB manufacturers and assemblers don't have these problems. But if we want the broader industry to return to the US – instead of getting piecemeal jobs – we need to be willing to provide a comparable level of service to that of the overseas competitors.

Undersecretary Lord properly defines the goal, but I believe her solution focuses too much on pricing and not enough on the customer experience. US assemblers need to open their arms to potential customers. It will help both them and the US manufacturing situation at the same time.

Otherwise, OEMs and other board

buyers will stick with offshore sourcing because they need to get their products built at a good price *and* in a timely manner. And "Made in America" will remain only a slogan from a bygone era.

venteclaminates.com

# Design for Rework: Extending the Usefulness of a PCB

Anticipate the assembler's needs in placement and routing.

WE ALREADY DESIGN for fabrication, assembly and test. DFx can be extended to thinking about future uses of an assembly. Sometimes a printed circuit board needs to be revised right away. There are things we can do to facilitate rework. Clearly marking all the components is a good start. A robust design will lend itself to touch-up and rework scenarios. Let's dive into some techniques.

Breadboarding for "science projects." Ever seen a breadboard? In PCB design terminology, a breadboard is a rectangle with a grid of plated through-holes set on the same pitch as a DIP package (FIGURE 1). The holes will accept axial-leaded components as well as the odd transistor package. Notice the rows of pins are tied together but can be cut as required by the mad scientist in the lab. Jumper wires on the leads create the rest of the circuit. Development boards can usually afford a slimmed down version of this.

FIGURE 1. A corner of the board can have a similar function for added development potential. Credit: Adafruit

No space for a breadboard? A rectangular region of the board can be set aside for a "dead bug." A component of any type can be glued to the board with the leads facing up. Then wires can be attached to the leads and connected as necessary. Another option uses a common component footprint placed on the board without any actual routing. A cap footprint can be placed at either end.

Two rows of pins can be placed side by side without a specific footprint in mind. One or both rows can have extra wide pins to accommodate the usual width, along with a wider package. The extended pads provide a location to attach a jumper wire. A second pair of rows can have a finer pitch. The idea is the geometry lends itself to different potential footprints, SO-8, SO-16, etc. It all depends on the component mix as to how future-proofing is implemented.

More generically, the solder mask can be strategically opened to allow a shunt cap or resistor to be placed along a transmission line. Again, different size phantom components can be added as the possibilities allow.

Typically, closed circuits can be designed with the option of becoming series elements. It's all the same net until the technician cuts the strap across the pads. Then a resistor, capacitor or ferrite bead can be installed in the component location. This wouldn't be great for a controlled impedance situation. It is, however, a common option when a power domain must branch out.

Joining two small pieces of metal together in an

oven is easy. All it takes is two pieces of metal and something that melts and then "wets" to both elements, which harden after coming out of the oven heating zone. Chocolate chip cookies come to mind (as they always do). Given a big enough chocolate chip, two cookies could be fused together, creating a crazy figure-8 cookie held together by chocolate. (Note to self: Expand on this two-for-one, high-chocolate ratio cookie idea next time we're going down the baked goods aisle.) That is not a

FIGURE 3. The additional bor-

der area enhances the jumper

FIGURE 2. Series elements

can be preplanned with com-

mon footprint geometry.

great metaphor for all the chemical transactions that occur on an SMT line but the effect is the same. Bring

JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for highspeed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly

JOHN BURKHERT

# Human-Augmentation Technologies are Worth the Risks

Advanced prosthetics highlight the value of pure research, with or without a business case.

I HAVE SAID this before, but I am a huge fan of technology's potential to help humanity, and particularly the opportunities to improve quality of life and restore impaired physical capabilities.

In my last column, I enthused about using augmented and virtual reality to create experiences and environments that help people interact and enhance their well-being. Physical augmentation, with technologies such as powered exoskeletons, have industrial and therapeutic applications and could also be used to help people with mobility problems get outdoors to tackle activities such as hill walking. Lack of mobil-

ity can have negative effects on the state of mind, as well as physical condition, so an assistive technology that tackles both these challenges could help us establish healthy approaches to aging and help us all keep engaged with the world around us for longer.

A prime applica-

tion for exoskeletons is to help people suffering from disability or limb loss reacquire important capabilities such as walking. Remarkable as these technologies are, there is enormous scope for improvement to make them easier to use and more affordable and therefore accessible to more people worldwide.

A lot of exciting work is happening in this area, particularly at the interface between academia and the many young startups spinning out of medical research projects. One that came to my attention is Mitt, which is connected with the Imperial Enterprise Lab at Imperial College London. Inspired by finding that some 50% of medical patients who receive a prosthetic give up after about one year because the limb is uncomfortable, difficult to use, and complicated to acquire and maintain, Mitt's team is developing high-tech solutions to improve wearers' experiences. It's not only the user interface - which, perhaps surprisingly, often comprises hooks and cables similar to the mechanisms used in prosthetics dating back as far as World War II - that is calling out for improvement. Affordability is a problem in the Western world, and even more so in the developing world, where limb loss is a greater problem. By leveraging technologies such as 3-D printing and smartphone-scale AI, we can hope these powerful restorative therapies become accessible to more than just a relatively privileged few.

Ideally, it would be best to control the prosthetic as easily and as naturally as a biological limb. Researchers have been developing brain-machine interfaces (BMIs) to achieve this, with limited success so far. Elon Musk's Neuralink initiative has sought to address some scalability issues that have restricted earlier BMIs to a relatively small number of channels and hence placed limitations on their speed and capabilities.

By developing robot-assisted processes to insert

"Engineering communities should take on projects for no better reason than because they can."

fine, flexible electrodes into the brain, without causing damage or being constrained by the presence of blood vessels, Neuralink aims to permit BMIs to have any number of channels for the electrode transmission from just a few to hundreds or thousands. It has also worked out a way of

inserting these quickly, using robotic tools, that could reduce the time for the process to just a few minutes. The electrodes are brought out to a device worn discretely behind the ear, which handles the processing and wireless connectivity that allows the wearer to control a device such as a computer or machine with their mind.

Neuralink is still in its early stages and may ultimately fall short of Musk's hype. However, this work could at least help standardize aspects of the BMI and thus contribute toward reducing the cost of advanced prosthetic controls.

The issue here is not the accuracy of Musk's claims but the value of the insights acquired. While Neuralink may or may not succeed, the body of knowledge within the scientific community continues to grow. This is the reason research must be allowed to continue without necessarily having a business plan behind it. Sometimes you have to start the journey before the destination becomes clear.

ambassador at Ventec International Group (ventec-group. com); alun.morgan@ ventec-europe.com.

**ALUN MORGAN**

is technology

continued on pg. 25

# How Big is Your Moat?

If the clearance is not at least 10 mils, yields may drop.

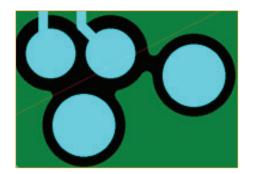

**ONE OF THE** often-overlooked aspects of a board design is the moat. Perhaps this conjures up images of Monty Python's *Holy Grail*, but moat does not refer to the ring around a castle. Instead, this is the clearance between pads and a surrounding copper plane, sometimes also referred to as embedded clearance.

These clearances often are 0.004" to 0.005" wide. This may seem like plenty of room, but Pareto analysis tells us this can lower overall manufacturing yield. These clearances often lead to unexpected yield loss, depending on certain design and processing factors. Believe it or not, etching these moats or clearances is difficult, due to the closed-ended, circular nature of the clearances. They do not image or etch well and are prone to shorting.

One reason is that driving the energy into the resist can result in bleeding and create an imaging short. But etching is also more difficult, as the etchant flow is trapped in a dead-end donut. These can conspire to create unintended image/etch shorts.

Mechanically there is potential for misregistration shorts, depending on the drill size, annular ring design and layer count. In such cases, the drilled and plated hole may short to the neighboring plane.

A good rule of thumb for mechanically drilled holes is to maintain at least 0.010" clearance from a drilled hole edge to any adjacent copper. This helps

ensure adequate mechanical clearance to account for layer misregistration, drill inaccuracies, as well as any internal etch-back or wicking in the hole. Note that this measurement is from drilled hole edge, not finished hole edge. Drilling is often 0.003" to 0.006" larger than the finished hole requirement to account for plating thicknesses and tolerances. This is where things end up tighter than expected if the designer does not account for drilled size compared to finished size.

Keep in mind there may be literally thousands of these embedded pad clearances on plane layers, especially as we see more HDI features. With multiple ground, power and

**FIGURE 1.** The clearance between pads and a surrounding copper plane is called a moat.

FIGURE 2. A larger moat could eliminate room for material between pads.

voltage planes, this adds up. The term DPMO (defects per million opportunities) comes to mind. If we reduce the number of these potential tight spots, yield improves.

Our first advice is to grow the clearances, if possible. Clearances of 0.006" or 0.007" are a substantial improvement for 1-oz. and thinner copper. If the layer is 2-oz. copper or thicker, we suggest another 0.0015" to 0.002" per ounce.

Sometimes this may present a challenge or two. If the moats get bigger, there may not be room for material between pads. That is fine, provided we don't leave isolated pieces of copper. Those can lead to slivers of copper that may come loose, or electrically floating planes. Completely remove any slivers. Review any isolated floating planes for opportunities to make at least one web connection to the larger plane.

In other cases, there may be signals between pads, and the plane is supposed to cover them. Here, do your best to thread the needle with signal trace and minimize the web between pads (FIGURE 2).

Beware the autorouter! It will not always center traces between pads (FIGURE 3). The autorouter will route signals to meet the minimum requirement, not the optimal solution. Often it will pack two traces between pads when it should or could have routed

> one to each side of a pad. This may not be perfect when it comes to impedance signals but in practice is likely to be overlooked in the system.

This is where a designer can maximize their impact by taking the time to center traces, as well as revisit how traces are routed between pads. Is there an alternate path that opens space to reduce the plane? Are traces moving efficiently between the pads? Many times, the angle the trace cuts between pads causes smaller spacing than necessary. Design diligence can result in a much higher yield and lower overall unit costs. The investment in design time will pay off in production.

Another option: Consider

**NICK KOOP** is director of flex technology at TTM Technologies (ttm. com), vice chairman of the IPC Flexible **Circuits Committee** and co-chair of the IPC-6013 Qualification and Performance Specification for Flexible Printed Boards Subcommittee; nick. koop@ttmtech.com. He and co-"Flexpert" MARK FINSTAD (mark.finstad@ flexiblecircuit. com) welcome your suggestions.

#### THE FLEXPERTS