5

HDP: Breaking the E-Glass Mold

#### PRINTED CIRCUIT pcdandf.com Licruitsassembly.com January 2021 DESIGN & FAB CIRCUITS CIRCUI

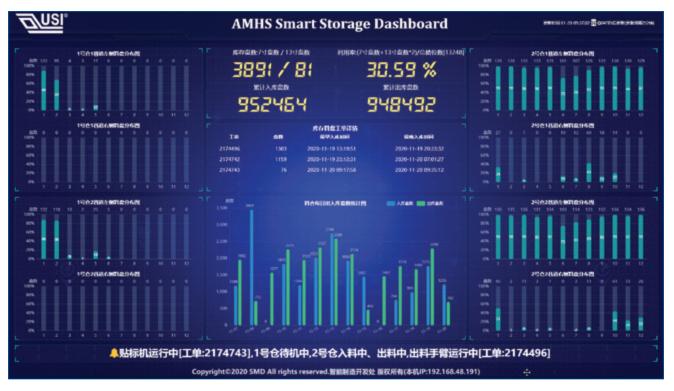

# All-Automated, All the Time at USI

0

IPC-DPMX

SiP Implementation

This issue of PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is brought to you by:

## **January 21, 2021** 1:00 – 4:00 pm EST

What Every Design Engineer Should Know About Design for SMT Manufacturability

# Phil Zarrow

\$75

Limited seating, register today!

pcb2day.com

Professional Development Certificate included!

TLB, a global leader in the 4th industrial revolution.

# **TRUST 2030**

Good Company in 20 Years, Great Company in 30 Years.

is specialized in manufacturing PCB for semiconductors. By joining World Class 300 in 2018, we have become a company specializing in materials and components leading the fourth industrial revolution. Based on technology and quality, we will establish ourselves as a material parts company that leads not only Korea PCB but also world PCB.

#### DRAM Module / SSD Module

IOT / Build-up Board

Semiconductor TEST B'd & 5G Network System

### TLB CO., LTD.

15602) 305, Sinwon-ro, Danwon-gu, Ansan-si, Gyeonggi-do, Republic of Korea Tel.82-31-8040-2096 Fax. 82-31-492-6623 Domestic Tel. 82-31-8040-2071, E-Mail. cmh@tlbpcb.com Offshore Tel. 82-31-8040-2060, E-Mail. will\_shin@tlbpcb.com

# PROTOTYPES IN 4 DAYS FROM TAIWAN

## **No Tariffs!** Best Quality and Price!

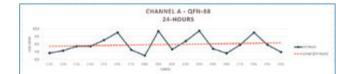

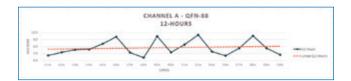

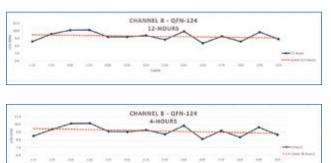

## Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

## Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

• SINCE 1986

www.PCB4u.com sales@PCB4u.com Tel: (408) 748-9600 2986 Scott Blvd., Santa Clara, CA 95054 SAM & ITAR Registered UL E333047 ISO 9001 - 2015

#### FIRST PERSON

#### 6 CAVEAT LECTOR

Fabricator blowout revisited? Mike Buetow

#### MONEY MATTERS

#### 12 **ROI**

The Covid- and people-free factory. **Peter Bigelow**

#### 13 BOARD BUYING

How to respond to supplier price increases. Greg Papandrew

#### TECH TALK

#### 14 DESIGNER'S NOTEBOOK

Estimating the PCB design cycle. John Burkhert, Jr.

#### 16 MATERIAL GAINS

From autos to airplanes, change is in the air. Alun Morgan

#### 17 MATERIAL MATTERS

A methodology for selecting the right material and the right price point. Bill Hargin

#### 40 GETTING LEAN

A near real-time feedback loop between layout and assembly. Hom-Ming Chang

#### 42 SEEING IS BELIEVING

What's more in need of rehabilitation? The bonepile or supplier gateway? Robert Boguski

#### 44 DEFECT OF THE MONTH

Intermittent area array packages. Bob Willis

#### 48 TECHNICAL ABSTRACTS

#### **DEPARTMENTS**

8 AROUND THE WORLD

- 11 MARKET WATCH

- 45 OFF THE SHELF

- 47 MARKETPLACE

#### JANUARY 2021 • VOL. 38 • NO. 1

## PRINTED CIRCUIT DESIGN & FAB CIRCUITS ASSEMBLY

#### **FEATURES**

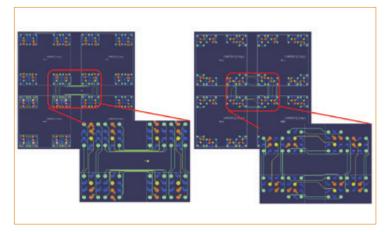

#### 19 DATA TRANSFER

#### New DfX Module for IPC-2581 Slices Design-Manufacturing Time, Errors

The latest IPC-DPMX standard offers unique bidirectional data exchange between design houses and their manufacturing partners. by HEMANT SHAH

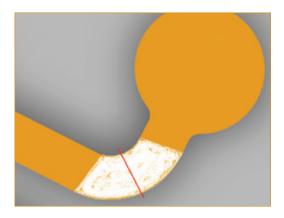

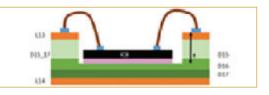

#### 22 CHIPLETS

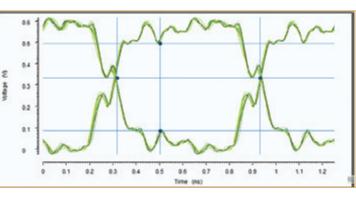

#### Evaluation of System-in-Package

#### Implementation Options in the Chiplet World

As chiplet usage increases, chip-level concerns shift into the area of systemin-package implementation. A case study of the cost vs. performance tradeoff. by STEVE WATT

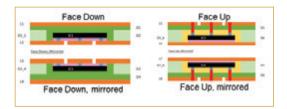

#### 24 HDP

#### Are Older Standards Still Valid, or Holding the Industry Back?

Despite the Covid-19 lockdown, HDP is coming off one of its most successful years yet, having completed 13 projects. New executive director Larry Marcanti and HDP facilitator John Davignon give an update of the consortium's latest work and future plans. by MIKE BUETOW

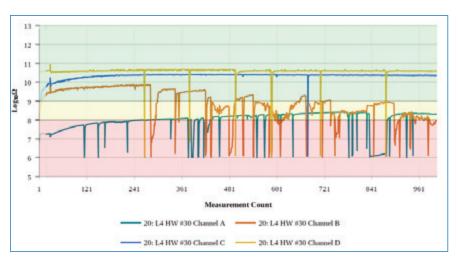

#### 26 ELECTROCHEMICAL RELIABILITY

## Process Control Plan to Monitor Acceptable Levels of Flux and Other Residues

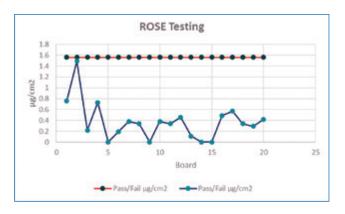

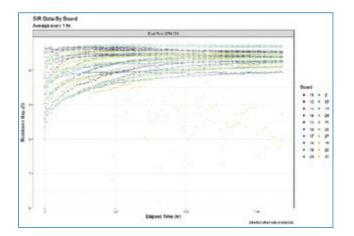

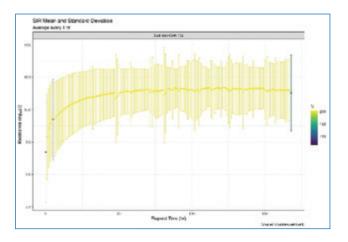

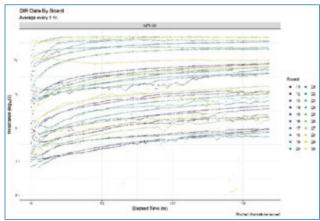

IPC J-STD-001G, Amendment 1, requires sampling plans to ensure soldering processes remain in control once qualified and validated. A well-vetted control plan that monitors the process and its performance on challenging components provides assurance that the process maintains control during the qualification stage. by BILL CAPEN, JASON EDGAR, DR. MIKE BIXENMAN, and MARK MCMEEN

#### 33 SMART MANUFACTURING *cover story*

#### Lights Out at USI

The EMS behemoth is on the cusp of an all-automated future. by MIKE BUETOW

#### IN THE DIGITAL EDITION

#### The Digital Route PCEA in the rearview mirror. by KELLY DACK

#### IEEC

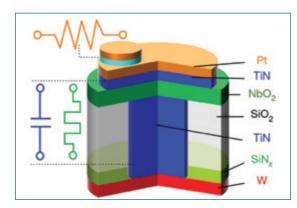

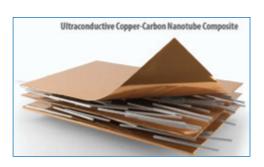

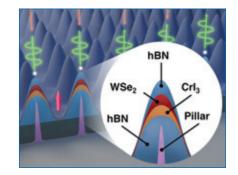

#### State-of-the-Art Technology Flashes Updates in silicon and electronics technology.

by BINGHAMTON UNIVERSITY

#### ON PCB CHAT (pcbchat.com)

CAF and Electrochemical Migration with GRAHAM NAISBITT

Changes in the Mainstream PCB CAD Market with MANNY MARCANO

#### Solder Voiding with TIM O'NEILL, PRAKASH GANGO and KALYAN NUKALA

POSTMASTER: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470, Canton, GA 30169

# Multilayer PCB Stackup

12 Layer Flex Rigid, 0.030" Thick Rigid, 0.008" Thick Flex Blind Via L1-L2 & L11-L12, 0.003" Hole, Resin Filled, 0.002"/0.002" Trace/Space, Controlled Impedance

Manufactured on August 2016

## When you're in a rush call RUSH PCB

Affordable Pricing \* Satisfaction Guarantee \* Fast Response \* Free Quote \* Fast Shipping HDI Boards \* Stacked Micro Vias \* 2 mil line & Space \* Flex & Rigid Flex

## Located in the Silicon Valley PCB up to 12 Layers in 3 days PCB Assembly Same Day Turn Full Turnkey Service

Certified: ISO9001/ITAR/UL www.rushpcb.com | Sales@rushpcb.com | 1 408 496 6013 Rush PCB Inc, 2149-20 O'Toole Ave, San Jose, CA 95131, U.S.A

### COMPREHENSIVE PCB DOCUMENTATION

Use 3D Models for Superior PCB Assembly Illustrations

Manage Layer Stackup Design and Materials

## BluePrint-PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings to drive fabrication.

of imported CAD data as a 3D PCB

Lowers documentation cost and time

Increases documentation detail & accuracy

Shortens PCB design cycles

Reduces documentation time by 60-80%

### downstreamtech.com • (508) 970-0670

©2020 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

## PRINTED CIRCL **DESIGN** & FA pcdandf.com

circuitsassembly.com

#### **EDITORIAL**

EDITOR IN CHIEF Mike Buetow 617-327-4702 | mbuetow@upmediagroup.com

SENIOR EDITOR Chelsey Drysdale 949-295-3109 | cdrysdale@upmediagroup.com

DESIGN TECHNICAL EDITOR Pete Waddell

EDITORIAL OFFICE P.O. Box 470, Canton, GA 30169

#### PCD&F CONTRIBUTING EDITORS

Akber Roy, Peter Bigelow, John Burkhert, Mark Finstad, Bill Hargin, Nick Koop, Greg Papandrew

CIRCUITS ASSEMBLY CONTRIBUTING EDITORS AND ADVISORS Clive Ashmore, David Bernard, Robert Boguski, John D. Borneman, Joseph Fama, Susan Mucha, Chrys Shea, Jan Vardaman, Ranko Vujosevic

#### PRODUCTION

ART DIRECTOR AND PRODUCTION blueprint4MARKETING, Inc. | production@upmediagroup.com

#### SALES

SALES DIRECTOR Frances Stewart 678-817-1286 | fstewart@upmediagroup.com

SENIOR SALES ASSOCIATE Brooke Anglin 404-316-9018 | banglin@upmediagroup.com EXHIBIT SALES

Frances Stewart 678-817-1286 | fstewart@upmediagroup.com PRINT/FLECTRONIC REPRINTS

banglin@upmediagroup.com

#### SUBSCRIPTIONS

For changes, additions or cancellations: subscriptions@upmediagroup.com

#### **UP MEDIA GROUP, INC.**

PRESIDENT Pete Waddell

VICE PRESIDENT. SALES AND MARKETING Frances Stewart

VICE PRESIDENT. EDITORIAL AND PRODUCTION Mike Buetov

DIRECTOR OF GROUP SHOWS

Alyson Corey | acorey@upmediagroup.com

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is distributed without charge to qualified subscribers. For others, annual Subscription Rates in U.S. funds are: \$80 (U.S. and Canada), \$145 (all other countries). Single copy price is \$8.50. All subscription and single copy orders or inquiries should be directed to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169, email subscriptions@upmediagroup.com. Photocopies and issues on Microfilm/Microfiche (16mm, 33mm or 105mm) are available from University Microfilms International, 300 N. Zeeb Rd., Ann Arbor, MI 48106, Telephone 313-761-4600.

PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY is published monthly by UP Media Group Inc., PO Box 470 Canton, GA 30169. ISSN 1939-5442. GST 124513185/ Agreement #1419617.

Periodicals postage paid at Canton/Ball Ground, GA, and additional mailing offices. © 2021, UP Media Group, Inc. All rights reserved. Reproduction of material appearing in PRINTED CIRCUIT DESIGN & FAB/CIRCUITS Assembly is forbidden without written permission.

Postmaster: Send address changes to PRINTED CIRCUIT DESIGN & FAB/CIRCUITS ASSEMBLY, PO Box 470 Canton, GA 30169.

# **READY TO ROLL IN 2021!**

Advanced Technology with World Class Engineering Support Diversified Offshore Supply Chain in Multiple Countries

#### DOMESTICALLY POISED FOR SUCCESS

- All Facilities Continue Covid-19 Free

- All 3 Shifts Intact and Complete

- New Capital Expenditures In Place

#### COMPLETE OFFSHORE SOLUTIONS READY

- Vetted Suppliers Across Multiple Regions

- Personnel Increase for Quicker RFQ Turnaround

- Bonded U.S. Warehouse for Tariff Mitigation

## Contact APCT | 408.727.6442 | APCT.com

Printed Circuit Board Solutions

APCT.com

APCT Santa Clara HQ APCT Anaheim APCT Orange County APCT Wallingford 408.727.6442

714,921,0860

714.993.0270

203.269.3311

**APCT Global** 203.284.1215

#### CAVEAT LECTOR

MIKE BUETOW EDITOR-IN-CHIEF

# *`Future Factories' Require Thinking `Smart' Today*

WENTY YEARS HAS passed since the US was a world leader in printed circuit board fabrication production. And not just in revenues, which tended to run neck-and-neck with Japan. The US also had the capability and capacity to build the largest-format boards in volume.

That was 2000.

I remember talking with Jack Fisher, then the technical director of the tech consortium ITRI, about the coming year. We were reviewing the latest bullish industry forecasts, in which some of the major fabricators were quoting lead-times of six to 12 months(!).

That unbridled optimism prompted Jack to observe that any hope of the US investing in HDI technology would be pushed out at least another year. Since order books were full for large boards, fabs saw no need to invest in next-generation technology.

Or so they thought. Because, as we all know, then the dot-com crash occurred.

It's hard to believe that was 20 years ago. But we might be edging toward history repeating.

Smart manufacturing, which is generally defined as the use of fully integrated, collaborative manufacturing systems that respond in real time to meet changing demands and conditions in the smart factory, in the supply network, and in customer needs, is quickly becoming reality.

It's been a long time coming. OEMs of assembly process equipment have long had the capability to see inside a customer's factory to perform software upgrades, view maintenance reports, and verify their machines were performing to spec. Manufacturer IT personnel, on the other hand, have historically resisted such intrusions to their networks. With IT and IP security recognized as intrinsic to operational success, most manufacturers have checked suppliers at the proverbial door.

In some of the largest EMS companies, that's changed, and it's working its way down to mid-tier companies as well. As we report in our cover story this month, Universal Scientific Industrial, which ranks 12th in the CIRCUITS ASSEMBLY Top 50, is all-in on an all-digital platform. Its Worldwide 5 Star Management System is bringing Industry 4.0 principles to every layer of the company. USI uses a common platform strategy to standardize the data automation protocols and equipment, and develop lead times and costs. They are making tremendous progress toward a true lights-out operation, having already reduced headcount in certain operations from the hundreds to single digits. AGVs move product from component stores to SMT lines several floors away, and inventory replenishment and vendor orders are triggered by software, not humans.

With its acquisition of AsteelFlash complete, USI can now roll out 5 Star to more than 25 manufacturing facilities worldwide.

As we reported in November, Lacroix Electronics is undertaking a similar transformation.

It has started work on the Symbiose smart factory in France, a greenfield project predicted to have 60% more output than similar-sized plants yet with the same number (450) of staff when it opens this year. The company is committing \$30 million toward a 205,000 sq. ft. (19,000 sq. m.) facility that it expects to generate annual revenues of more than \$120 million. Lacroix will use industry-developed open source IoT communications standards for its digital factory.

At its Shanghai smart factory, USI builds SIPs for smartwatches. Lacroix is heavily vested in automotive. Both are lower-mix, high-volume segments. It is predictable, then, that domestic North American assemblers will say, "Good for them, but it doesn't apply to me."

That's what we heard from fabricators two decades ago.

One person who has studied the implementation of the smart factory matter deeply over the past year believes the US is five to seven years behind Europe and as much as 10 years behind the leaders in Asia.

How many fabricators wish they could go back in time and invest in a laser drill or five? The US misplayed the technology game at immense cost to the region. The idea that assembly is somehow insulated from a similar outcome is wholly misguided.

The US shouldn't cede entire markets, as it currently does with consumer and mobile, thinking that aerospace, defense and medical are permanently sustainable and impervious to foreign competition. Fabricators learned the hard way that you can't always depend on what you have now.

Instead of saying, "Convince me," it would behoove North American shops to say, "Catch me up." And then act accordingly.

mbuetow@upmediagroup.com @mikebuetow

P.S. We are pleased to bring back the PCB East conference and exhibition to the Boston area in May. Check out the details at pcbeast.com.

The **ORIGINAL** Conference and Exhibition for Printed Circuit Board Design, Fabrication and Assembly on the **EAST COAST**.

Conference: May 10 - 12 Exhibition: Tuesday, May 11

Best Western Royal • Plaza Hotel & Trade Center Marlborough, MA

## WHO'S ON BOARD?

#### PCDF People

Altair appointed Matthew Brown senior vice president and chief financial officer. Brown previously served in finance leadership roles at NortonLifeLock, including as inter-

im CFO from November 2019 to July 2020.

Altium promoted **Christopher Donato** to head of digital channel. He's been with the company in account management and sales positions since 2004.

CMR Surgical named **Jesus Castane** senior PCB engineer.

Kent Balius and Ken Smythe have launched EPIC Front-End Engineering.

#### **PCDF Briefs**

Amazon has shifted part of the computing for its Alexa voice assistant to customdesigned chips, aiming to make the work faster and cheaper, while moving it away from chips supplied by Nvidia.

Apple has selected WLCSP/fan-in for its latest iPhones. Apple is expected to ramp up flexible circuit demand for its 2021 devices, and is looking to work more closely with ZDT, Compeq, Unimicron and Career Technology, according to reports.

Amphenol will acquire MTS Systems for approximately \$1.7 billion, including assumption of outstanding debt and liabilities, net of cash.

**Calumet Electronics** is expanding its PCB manufacturing operations in Michigan to meet market demand.

China is stepping up the development of homegrown EDA software and systems as part of its efforts to boost self-sufficiency in semiconductor, and many EDA startups have become operational with government subsidies, according to reports.

**Delta Sigma** will use **Zuken's** Harness Builder for E3.series for its electrical harness design.

Firan Technology Group achieved Nadcap accreditation and certification at its PCB manufacturing facility in Fredericksburg, VA.

**IMI Inc.** successfully completed an intensive audit to IPC-1791, *Trusted Electronic Designer, Fabricator and Assembler Requirements* and has earned a Qualified Manufacturer's Listing under IPC's Validation Services program.

**Jingwang Electronic Technology's** new 157,000 sq. m., \$175 million PCB fabrication campus is expected to open this year.

### 3D Glass Solutions, Nokia Collaborate on D-Band Signal Transport

**ALBUQUERQUE, NEW MEXICO** – 3D Glass Solutions collaborated with Nokia to deliver D-band signal transport. D-band signal transport requires integrated mm-wave modules with high spectral-efficiency. 3DGS worked with Nokia to develop a demonstrator for ultra >30Gbps speed wireless backhaul systems.

"This solution allows designers in D Band TX/RX modules the lowest loss and lowest cost point for TX/RX modules, as demonstrated by this radio-on-glass architecture for Nokia, operating up to 160GHz with less than 1dB of loss from the chip to the antenna output/input ports," said Jeb Flemming, CTO, 3DGS.

"One of the reasons we've been able to achieve such extraordinary performance numbers using our RFIC on glass is because we've been working closely with the engineers at 3DGS," said Shahriar Shahramian, director of sensing and communication ASICs research, Nokia Bell Labs. "Its unique etching process allows us to build things on glass that simply aren't possible using any other process. At the same time, 3DGS' willingness to collaborate and explore unexplored areas and applications has allowed us to build something incredible."

"This is the next generation of ultra-high-performance radio-on-glass modules operating at these frequencies," said Flemming. "Our demand for data continues to grow, and we are pleased to work with Nokia to deliver record-breaking solutions that can keep up with that demand." (CD)

## Altium to Sell Tasking Business to PE Firm

**SAN DIEGO** – Altium will sell its Tasking business unit to a private equity group for more than \$100 million in what the ECAD company is calling a "strategic divestment." FSN Capital, a European private equity firm, will pay up to \$110 million for Tasking, \$10 million of it conditional on the company hitting certain revenue targets in the 2021 financial year.

The deal will close in the second half of Altium's current fiscal year, which ends in June. Altium will instead focus on its PCB design software.

Tasking produces embedded systems development software. The unit recorded flat sales of \$20 million in Altium's fiscal 2020 due to Covid-related market issues.

"While Tasking is a great business, it does not play a central role in our design to realization strategy for the electronics industry, which is being delivered through our new cloud platform, Altium 365," Altium said in announcing the deal.

"The strategic divestment of Tasking, combined with our recent organizational changes and hard pivot to the cloud, marks an inflection point for Altium in its pursuit of industry transformation," said Aram Mirkazemi, chief executive, Altium. "The divestment of Tasking will free up organizational capacity and allow Altium leadership to focus on our main game, which is to expand Altium 365 and accelerate its adoption."

Altium acquired Tasking in 2001.

On Nov. 19, Altium guided for fiscal 2021 full-year revenue of \$200 million to \$212 million. Announcing the Tasking deal, it reiterated that guidance, less Tasking, implies a lower forecast for its PCB tools going forward in calendar 2021. (MB)

## Infinera Wins Best Overall Design in Mentor's PCB Design Awards

**WILSONVILLE, OR** – A team from Infinera and Jabil has been selected as designers of the best overall circuit board by a group of industry experts under the auspices of Mentor. (Mentor is now officially Siemens EDA.)

Now in its 28th incarnation, the PCB Technology Leadership Awards recognize engineers and designers who use innovative methods and design tools to address

complex PCB system design challenges and produce industry-leading products.

The contest is open to any designs created with Mentor PCB solutions. Judging is based on design complexity and overcoming associated challenges, such as small form factors, high-speed protocols, multi-discipline team collaboration, advanced PCB fabrication technologies, and design-cycle time reduction.

Experts in the PCB industry judged entries from around the world in categories representing computers, blades and servers, memory systems; consumer electronics and handheld designs; industrial control, instrumentation, security and medical applications; military and aerospace solutions; telecom, network controllers, line cards; transportation and automotive designs.

The panel of judges this year included Dr. Rajan Bedi, Stephen Chavez, Mike Creeden, Gary Ferrari, Rick Hartley, Steve Herbstman, Happy Holden, Pete Waddell and Susy Webb. (CD)

## Emerald EMS Acquires Saline Lectronic, Veris Manufacturing

**SALEM, NH** – Emerald Electronics Manufacturing Services has acquired a pair of electronics manufacturing service providers, extending its range to the Midwest US and adding capacity in Southern California. The deals also expand the EMS company's reach into the defense and medical end-markets.

Both Saline, MI-based Saline Lectronics and Brea, CA-based Veris Manufacturing are manufacturers of high-mix, low- to medium-volume printed circuit board assemblies and box-builds for high-reliability end markets, including industrial controls, aerospace and defense, and medical.

"All of us at Emerald are excited about the expanded geographic reach and manufacturing capabilities that Saline Lectronics and Veris Manufacturing bring to the mix," said Vic Giglio, chief executive, Emerald EMS. "Their addition expands the Emerald EMS footprint into Southern California and the Midwest domestically, bringing increased geographic flexibility and expanded capacity to all of our customers."

Founded in 2002, Saline is a full-service electronics solutions company with a 110,000-sq. ft. manufacturing facility providing engineering, PCB assembly, testing, electromechanical box build, and direct fulfillment for the industrial controls, aerospace and defense, medical and oil industry end-markets.

Originally known as Quality Control Manufacturing, Veris was founded in 1987. The company's 40,000-sq. ft. facility provides manufacturing and engineering services focused on the aerospace and medical end-markets.

"Our partnership with Emerald EMS will allow us to offer our customers expanded capacity, as well as access to lower-cost options through Emerald's Shenzhen, China, manufacturing facilities, while Emerald gains a strong Midwest presence," said Mario Sciberra, president and CEO, SLI.

"Joining Emerald expands our access to new markets and provides investment opportunities for us to build on our capabilities in order to stay ahead of the demands of our growing customer base," said Jay Cadler, president, Veris.

Day-to-day operations are expected to remain unchanged at both SLI and Veris, which will continue to operate under their existing brand names under the Emerald umbrella, Giglio said.

Emerald EMS was formed in July 2020 through the acquisitions of Data Ed and Bestronics by New Water Capital, a Chicago-based private equity firm. (MB)

#### Syrma Technology, SGS Tekniks Merge

**SAN JOSE** – Syrma Technology in November merged with SGS Tekniks in a cash and stock deal of Indian EMS companies.

Syrma SGS Technologies will have a combined revenue of more than Rs 10 billion (\$134 million). Some 55% of revenues are from exports to the US and Europe. MKS Instruments has received an order for multiple ESI Geode HDI laser drills in Taiwan.

Nano Dimension announced an additional 10 customers owning one or more older DragonFly Pro machines have upgraded to the next-generation DragonFly LDM machines.

SiC technologies are gaining the confidence of many customers and are penetrating various applications, especially electric vehicles, a new report claims.

University of Southampton's Optoelectronics Research Centre demonstrated an all-silicon optical modulator at 100Gb/s and beyond, without the use of digital signal processing.

**Ventec** has passed the ISO 9001:2015 audit for its Quality Management System at its facility in Fullerton, CA.

Zuken and Electro Magnetic Applications have entered a partnership to improve the accuracy of cable harness simulation models for complex electrical subsystems in aircraft and vehicles.

#### CA People

Benetel named **Alan Hynes** director of engineering.

Creative Electron named **Jeff Darby** vice president of business development.

Enics appointed **Kristiina Leppänen** chief financial officer. Prior to joining Enic, Leppänen was CFO for Cavotec, among other executive positions.

Nordson Test & Inspection named **Dennis Rutherford** general manager, rest of Asia. He joined Nordson in 2016 after 15 years in high level sales positions with electron-

ics inspection OEMs.

Fred Dimock recently started Fred C Dimock Global Services, focusing on thermal processes and profiling. He spent the previous 20 years as manager, process technology at BTU.

Japan.

vious 20 years as manager, process technology at BTU. Yamaha appointed Nick Isomura division manager of the Intelligent Machinery (SMT Equipment and Robotics)

Division. He has more than 20 years' experience in SMT equipment sales, and previously was group manager of Europe, Southeast Asia and Americas SMT sales for Yamaha in

Zestron named James Mueller Western regional sales manager. He has over two decades of professional sales management success, 12 years of which has been centered on

achieving sales growth within the precision and critical cleaning marketplaces.

#### **CA Briefs**

Absolute EMS installed a Hanwha HM520 SMT line.

AIM Solder opened a 12,000 sq. ft. ISO 9001-certified solder manufacturing facility in Malaysia.

Amazon has laid off dozens of R&D and manufacturing staff from its delivery drone project, Amazon Prime Air, and will outsource production.

**Apple** has reportedly started sending foldable iPhones to **Foxconn** for testing, with a possible release in September 2022.

Apple's plans to move the production of devices away from China received a major upswing, with several partners entering India through the government's Production-Linked Scheme (PLI).

SMIC and China Electronics Technology Group are among more than 30 companies blacklisted by the Trump administration for their suspected ties to the Chinese military. CETG is the parent of TPV Technology and Shenzhen Kaifa, two of the largest ODM/EMS companies in the world.

**Chase Corp.** finalized the acquisition of **ABchimie**, a developer of coatings for electronics, in an all-cash deal.

**Cogiscan** announced a strategic partnership with **Mycronic** to provide machine connectivity for Industry 4.0 applications.

**Creative Electron** has been awarded a patent for Al-powered programming of x-ray inspection systems.

Datest announced a new technical partnership with Aster Technologies.

Ease announced the availability of a complimentary new ebook, *The Ultimate Guide to Layered Process Audits*, which details layered process audits and offers advice, checklists and tips and tricks. (https://go.ease.io/Ultimate-Guide-to-LPAs\_LP.html)

**Eolane** acquired a **Kurtz Ersa** Versaflow 4/55 selective soldering oven for its Valence Romans Agglo site.

**Foxconn** is not expected to receive tax credits from Wisconsin in the next three years, according to the state Department The combined company aims for 20% year-over-year growth.

The companies did not disclose any financial terms of the deal.

Syrma SGS Technologies will have eight manufacturing facilities in India and three design centers, including in Chennai and Gurgaon, India, and Stuttgart, Germany. Currently, Syrma and SGS each have four factories in India.

Syrma designs and manufactures RFID technology, power electronics, and turnkey manufacturing services and custom magnetics, and delivers IoT products for the automotive, computing, industrial, medical, power, and telecom companies. Medical and defense electronics are surging, the firm says. (CD)

of Administration.

**Foxconn** said a facility in Mexico has returned to normal following a ransomware attack in December. It also confirmed it has placed a bid to take over a stake in foundry **Silterra**.

**Indium** and **Valuetronics** have formed a strategic partnership to serve customers in the Americas with their cored wire, rework fluxes, and bar solder products.

Intellitronix acquired a SpeedPrint 700 series screen printer and Europlacer iineo+ pick-and-place system, and Universal Instrument model 5362i conveyors.

**Intervala** is reportedly considering a move in Pittsburgh that would increase its footprint from 136,500 sq. ft. to about 220,000 sq. ft.

KIC appointed Rocka Specialty Solutions manufacturers' representative throughout Mexico.

Mentor will now be known as Siemens EDA. The company will continue to operate as part of Siemens Digital Industries Software.

Fresh off its acquisition of **Tabtronics** in November, **Mirac** announced plans to will build an 11,800 sq. ft. EMS plant in Manchester, OH.

Mountain Electronics acquired ALJ Electronics/ALJCO.

**MRSI** and **Palomar Technologies** have reached an agreement that settles all litigation currently pending between the companies.

**NexLogic Technologies** added a 3,000 sq. ft. Class 10,000 clean room to its EMS operations in San Jose.

**Nordson Dage** named **Murray Percival** representative of its Assure series of x-ray component counters in the Midwest US.

**Northrop Grumman** awarded **Kitron** a three-year, NOK 20 million (\$2.2 million) contract to update a F-35 test program set and provide a repair capability.

**NovaCentrix** appointed **Torenko & Associates** rep in Texas, Oklahoma, Louisiana, Arkansas and the interior of Mexico.

**PDF Solutions** has entered into a definitive agreement to acquire **Cimetrix** for a \$35 million cash payment, net of cash, and subject to other closing adjustments.

**Pegatron's** board has approved an initial investment of \$150 million for building manufacturing facilities in India.

**Qualcomm** received a license from the US government to sell 4G mobile phone chips to **Huawei**, an exemption to US trade restrictions imposed amid rising tensions with China.

Saki opened the Saki Virtual Showroom, a digital reproduction of the Solution Center housed in its Tokyo headquarters.

SEMI submitted comments to the US Department of Commerce urging caution and the adoption of regulatory best practices and microelectronics industry recommendations to ensure its identification of foundational technologies does not restrain US innovation and exports without furthering essential US national security interests.

**South-Tek Systems** appointed Torenko & Associates manufacturers' rep in Mexico.

**TT Electronics** has completed the acquisition of **Torotel**, a manufacturer of power and electromagnetic assemblies and components for the aerospace and defense markets.

**TT Electronics** opened an electronics manufacturing facility in Kuantan, Malaysia.

Universal Scientific Industrial in December completed the acquisition of Asteelflash through the acquisition of its parent company, Financière. USI also broke ground on a 65,000 sq. m. facility in Haiphong City, Vietnam, with a planned investment of \$200 million for phase one.

Vantage Specialty Chemicals named Creyr Innovation manufacturers' representative for its surface treatment technologies.

#### EDITED by CHELSEY DRYSDALE

| OUT OF STORAGE                                                                                                                                               |      |               |      |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|------|

| Trends in the US electronics<br>equipment market (shipments only)                                                                                            | AUG. | % CHA<br>Sep. |      | YTD% |

| Computers and electronics products                                                                                                                           | 0.5  | 1.6           | 2.2  | 3.5  |

| Computers                                                                                                                                                    | -0.7 | 4.3           | 1.7  | -8.5 |

| Storage devices                                                                                                                                              | -1.3 | -5.2          | 17.5 | 33.5 |

| Other peripheral equipment                                                                                                                                   | 3.0  | -7.9          | 2.1  | 9.5  |

| Nondefense communications equipment                                                                                                                          | 1.7  | 2.8           | 10.6 | 11.3 |

| Defense communications equipment                                                                                                                             | 6.2  | -5.1          | -0.4 | 5.9  |

| A/V equipment                                                                                                                                                | -3.0 | 4.0           | 1.6  | -5.3 |

| Components <sup>1</sup>                                                                                                                                      | 0.7  | 0.3           | 0.9  | 10.0 |

| Nondefense search and navigation equipment                                                                                                                   | -0.8 | 0.0           | 2.6  | -5.7 |

| Defense search and navigation equipment                                                                                                                      | -3.2 | 2.9           | 0.8  | 2.5  |

| Medical, measurement and control                                                                                                                             | 2.8  | 1.1           | 1.7  | -1.1 |

| <sup>r</sup> Revised. *Preliminary. <sup>1</sup> Includes semiconductors. Seasonally adjus<br>Source: U.S. Department of Commerce Census Bureau, Dec. 4, 202 |      |               |      |      |

| US MANUFACTURING INDICES             |                   |      |      |      |      |  |  |  |

|--------------------------------------|-------------------|------|------|------|------|--|--|--|

|                                      | JUL.              | AUG. | SEP. | OCT. | NOV. |  |  |  |

| PMI                                  | 54.2              | 56.0 | 55.4 | 59.3 | 57.5 |  |  |  |

| New orders                           | 61.5              | 67.6 | 60.2 | 67.9 | 65.1 |  |  |  |

| Production                           | 62.1              | 63.3 | 61.0 | 63.0 | 60.8 |  |  |  |

| Inventories                          | 47.0              | 44.4 | 47.1 | 51.9 | 51.2 |  |  |  |

| Customer inventories                 | 41.6              | 38.1 | 37.9 | 36.7 | 36.3 |  |  |  |

| Backlogs                             | 51.8              | 54.6 | 55.2 | 55.7 | 56.9 |  |  |  |

| Source: Institute for Supply Managem | ent, Dec. 1, 2020 | 1    |      |      |      |  |  |  |

| KEY COMPONENTS                                |       |       |       |                         |                           |  |

|-----------------------------------------------|-------|-------|-------|-------------------------|---------------------------|--|

|                                               | JUN.  | JUL.  | AUG.  | SEP.                    | OCT.                      |  |

| Semiconductor equipment billings <sup>1</sup> | 14.4% | 26.7% | 32.5% | <b>40%</b> <sup>r</sup> | <b>26.9%</b> <sup>p</sup> |  |

| Semiconductors <sup>2</sup>                   | 4.9%  | 4.23% | 4.94% | 5.79% <sup>r</sup>      | 5.95% <sup>p</sup>        |  |

| PCBs <sup>3</sup> (North America)             | 1.12  | 1.00  | 0.94  | 0.93                    | 0.97                      |  |

| Computers/electronic products <sup>4</sup>    | 5.44  | 5.28  | 5.22  | 5.15 <sup>r</sup>       | 5.00 <sup>p</sup>         |  |

Sources: <sup>1</sup>SEMI, <sup>2</sup>SIA (3-month moving average growth), <sup>3</sup>IPC, <sup>4</sup>Census Bureau, <sup>p</sup>preliminary, <sup>r</sup>revised

### Hot Takes

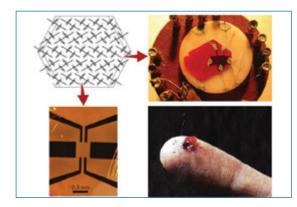

- The global wearables market grew 35.1% year-over-year during the third quarter, with total shipments reaching 125 million units. (IDC)

- Flexible hybrid electronics is expected to be an approximately \$3 billion market by 2030. (IDTechEx)

- Desktop and notebook PC shipments are expected to grow 18% year-over-year in the fourth quarter, followed by 1.4% growth in 2021. (IDC)

- Smartphone shipments are forecast to grow 2.4% year-overyear in the fourth quarter, followed by 4.4% year-over-year growth in 2021. (IDC)

- The market for high bandwidth memory is projected to grow 49% in wafers, including DRAM and logic layers, from 2020 to 2024. (TechSearch International)

- Third-quarter world electronic equipment shipment growth

was down an estimated 1.4% compared to the same quarter in 2019. (SEMI)

- India has 268 mobile and accessories factories, more than twice the number often quoted by many senior leaders in the government. (India Cellular & Electronics Association)

- Fiberglass yarn and fiberglass cloth materials for PCBs saw a 20% increase in quotes, reflecting strong demand for 4.5G and 5G applications. (TPCA)

- India has the potential to become a \$100-billion global manufacturing and export hub for printed circuit board assembly by 2025-26. (ICEA)

- The worldwide telecom EMS market was worth \$155.7 billion in 2019 and is projected to grow at a CAGR of 7% from 2020 through 2027. (Statista)

- Worldwide server shipments declined 0.2% year-over-year to nearly 3.1 million units during the third quarter. (IDC)

### **Revealed: Technology Really Works!**

Now, just how many people can we move off the floor?

THIS PAST YEAR was most unusual, distracting and challenging, and many of those distractions and challenges appear they will remain with us well into the first half of the year. As industry begins to focus on post-pandemic planning, however, much has been learned over the past year that can and is being applied to planning for the future.

Possibly the most significant thing learned is technology can – and does – work! A generation of manufacturing and technology leaders knew little of platforms such as Zoom, WebEx, etc. Through baptism by fire, we have become believers in virtual interaction, its effectiveness and value. Equally significant is the realization that for many business functions, including those in manufacturing, remote working – aka working from home – works and offers much more flexibility than the traditional structured workplace.

Manufacturers have by necessity reconfigured shop floors to accommodate social distancing, cleaning protocols, and all that has gone with the Covid pandemic. Adding space between production lines can accommodate social distancing. But while effective, it has proven costly. Splitting shifts is another tactic. Employees may be willing today to change schedules to keep a job; however, it is not ideal in the long term. Meanwhile, in the office environment social distancing is accomplished via interactive technology. Further, many claim the efficiency and flexibility from employees working remotely and communicating virtually has been significantly better than they imagined. The office environment success and flexibility from harnessing virtual communication technology has not gone unnoticed by the manufacturing manager.

Over the past couple months, I have had many conversations with colleagues in our industry and other manufacturing fields about how to apply the lessons learned as we attempt to return to "normal," or as a "new normal" emerges. Much of the conversation has focused not on how to reduce headcount and therefore costs, but instead on how to reduce the "traffic" and "parking" on the shop floor via harnessing virtual interaction technology to increase efficiency and reduce process time. One of the observations I keep hearing is that with fewer people congregating on the shop floor at the same time, product seems to move faster through work cells and from process to process.

Further discussion has centered on rethinking manufacturing processes: separating the "hard" tasks of manufacturing, which require an onsite human operating a piece of equipment and touching product, from the "soft" tasks, which are often monitoring processes, verifying and validating product, and generating documentation. On a traditional shop floor these tasks take place side-by-side by different employees with different skill sets.

The thought is if those responsible for the "soft" tasks do them remotely, it will reduce shop-floor traffic. Less traffic means fewer distractions and greater flexibility, and there is less opportunity a "parking lot" will develop as people chit-chat, reducing throughput and efficiency. Wherever traffic is, you frequently end up with an area filled with inert employees and products.

Performing those "soft" tasks virtually, however, requires more than just a Zoom account. And that's where creative process engineers are working to harness sensors, test and measurement equipment and basic automation with the anticipation that a reasonable happy medium can be achieved.

For years it has been possible to monitor equipment such as drill machines remotely. Likewise, computer-driven CMM equipment can be operated offsite. Ditto for verification documentation, such as a FAI. Employees who handle these tasks from home or in a cubicle off the shop floor will continue to be the norm. But much of the other tasks in manufacturing are more challenging.

High-volume manufacturing offers some opportunity to lean out the shop-floor traffic as well. More than a few process engineers are looking at how to reduce the number of people in a work cell by locating one or a few off the shop floor, while they still monitor the process or line. Staggering work-cell schedules, not by multiples of shifts but by minutes, can also separate setup from operators from test and verification, collectively reducing shop-floor traffic.

High-mix, low-volume manufacturing environments have the greatest challenge to deploying virtual interactive technology to reduce shop-floor traffic. And more opportunities exist. Creating data and tooling packages can be done remotely, as can much of the end verification and validation data creation. Staging work through a network of onsite and offsite staff – implemented thoughtfully – can increase flexibility and throughput and reduce traffic.

Finally, for those who thought Industry 4.0 was interesting, much of the past year has provided validation that the technologies are in place and work well. Many colleagues are moving feverishly to take advantage of the available tools now that employees and managers – many who have never imagined utilizing such technology – are experiencing their power and convenience on a personal and professional level.

PETER BIGELOW is president and CEO of IMI Inc.; pbigelow@imipcb. com. His column appears monthly.

## PCB Costs Are Going Up. Here's What to Do

How to respond to supplier price increases.

DEMAND FOR PRINTED circuit boards is going up. But so are production costs.

Raw PCB material pricing has jumped about 40% since June, with the exact increase dependent on material type. This price increase was inevitable and is, in fact, overdue.

During the early months of the Covid crisis, most PCB suppliers were hesitant to pass on their alreadyincreasing material costs. But as China has rebounded faster from the Covid slowdown than the US and Europe, demand for production has escalated. PCB vendors are now more willing to pass higher material costs onto their customers. And the price increases are by no means over.

The price of gold salt and the precious metals used for metallic finishes of the PCB are on the rise as well. While the cost for the application of ENIG finish is the same regardless of the layer count, the percentage of price increase is inversely proportional to the PCB layer count, meaning a double-sided board will see a higher percentage price increase than a 10-layer PCB.

To add insult to injury, American buying power has fallen almost 6% since January as the value of the US dollar has declined against the Chinese RMB.

When it comes to PCB costs, we are in a perfect storm. The price of raw materials, gold and precious metals is on the rise, along with production demand. At the same time, the dollar is weaker. That means higher prices for US PCB buyers.

Here's the bottom line: You can expect over the next few months to see an additional price increase of eight to 10% for doubled-sided boards, depending on technology and quantity requirements. Multilayer PCBs are expected to rise five to eight percent.

However, PCB buyers may be able to fend off some of those increases by buying smarter and more strategically.

Putting PCBs in an array for ease of assembly makes sense, but I can't tell you how many times I have seen wasted circuit board real estate when it comes to panelization design. More square inches mean a more expensive board. Buyers need to push back on their production and engineering departments by asking questions such as, "Does this array really need to have rails this wide?" or "Can we score instead of route?"

Does every board you buy require a gold finish? Yes, ENIG is lead-free; it has great coplanarity features and a long shelf life. But does every assembly on your production floor really need all those costly benefits?

Don't allow a boilerplate company standard to unnecessarily inflate costs. Be selective. Use a premium finish only when truly necessary. From a pricing standpoint, there is more than one "metallic" way to assemble a PCB.

Do you order the same part number and quantity monthly? If so, review those repetitive purchase orders and have a heart-to-heart talk with your customer. Your PCB vendor would prefer to run a larger quantity when and wherever possible. Ordering a larger quarterly quantity of PCBs and accepting them in monthly deliveries is a great way to get a discount.

Also, start leveraging your PCB spend with your vendors. Have them visit (for now, you may have to conduct a virtual meeting) and ask what else you can do to reduce costs. At the same time, remind them of your annual spend and length of business relationship. Have a serious discussion about performance issues. If your supplier intends to raise prices, demand those increased costs come with enhanced service.

Keep in mind, though, that the best way to keep pricing in check is to always pay your PCB vendors on time. Timely payment will dictate the strength of your relationships with suppliers. Habitually paying beyond the agreed-upon terms can harm your business relationship in a variety of ways, including lowering your level of customer service, giving you less favorable payment terms in the future, and increasing your pricing.

The more you string out payments to vendors, the less likely those vendors will be to jump through hoops – bending to price pressures, responding quickly when an expedite is needed, or acting to resolve a quality problem – when you need them to.

It always surprises me when a PCB buyer gets upset when I inquire about late payment. If one of *my* PCB shipments were late, that same customer would demand to know its whereabouts. Just as you as a buyer demand prompt delivery of product, you should also be a consistently prompt payer.

A customer who doesn't pay is not really a customer. That applies to your company as well. Paying your PCB vendors on time increases their confidence in you as a business partner, and you will reap the benefits of that confidence over and again. It's a big part of fostering a good relationship with your vendors, and it makes it much easier to get price concessions, even during tough times.

#### GREG

PAPANDREW has more than 25 years' experience selling PCBs directly for various fabricators and as founder of a leading distributor. He is cofounder of Better Board Buying (boardbuying.com); greg@boardbuying. com.

# Estimating the PCB Design Cycle with Limited Information (and Then Making It Happen)

What Charlie Brown can teach us about board design.

NOT ALL BOARDS are alike. In fact, no two are exactly the same. That's kind of the point. We always do something that hasn't been done before, or we wouldn't be doing it. The best we can say is many boards share similarities. Just the same, someone in every organization wants to know when the one-off job will be completed.

Often, there is a predetermined schedule in which someone who has never drawn a trace decides when the PCB layout needs to be finished. Such a schedule is usually the result of market forces. It could be backto-school, CES, or even (especially) a rocket launch date that drives the deadline. Still, it's not unusual for stakeholders to ask your opinion about the estimated tape-out date.

#### Life in a service bureau or as an outside contrac-

tor. Service bureaus live or die by the accuracy of their bids. If their bid is too many hours, the customer will shop around. If the bid is too few, the designers end up eating that cost with overtime or, worse, missing the date and facing customer dissatisfaction. The one thing that saves them is that the service bureau is working from a baseline plan that does not usually include codevelopment.

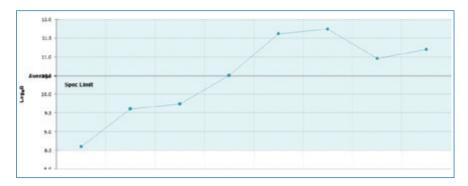

A statement of work including a few milestones will put the customer in lockstep with the vendor. A definition of success that includes the delivery date will also have a few intermediate milestones, including schematic capture, mechanical lockdown, placement approval, and so on (FIGURE 1). The hourly amount the service bureau charges is more than it pays the designer. Even in a one-person shop, overhead comes first, and the owner-operator gets paid out of the remaining funds.

I once owned one of those operations. The worst possible outcome was that I would have to subcontract work out. In that case, it was more like being a broker than a designer. If my plate was full, I would no-bid a proposal or quote a-higher-than-normal rate. Getting a lot of business in a short amount of time is a mixed blessing.

The mid-design updates trigger an ECO charge that can be quite substantial. The incentive is to quote an aggressive but doable schedule. Once underway, the plan is to tack on fees if the design cycle is interrupted by improvements. Some customers appreciate they are spending money to pull in the launch date. You want repeat customers, so be careful not to overextend yourself.

One of the main metrics in the design cycle is the number of pins. Back in the day, it was a dollar per pin. Some pins matter more than others. A length-matched pin counts as three pins because you take more time to dial it in with the rest of the bus. RF pins are twofor-one because of the expected back-and-forth with the analog engineer. As you build your portfolio, take note of the actual vs. estimated duration so you can fine-tune your scheduling quotes.

New component footprints, whether built in the CAD tool or imported from a vendor or library service, take time. You must take them into account for the estimate. Of course, not all components are created equal. Higher pin-count and fine-pitch devices are another weighting factor in the pin-count. Board density is in play, too. Test fixtures will usually go more quickly than production form-factors. The stack-up

JOHN BURKHERT JR. is a career PCB designer experienced in military, telecom, consumer hardware and, lately, the automotive industry. Originally, he was an RF specialist but is compelled to flip the bit now and then to fill the need for highspeed digital design. He enjoys playing bass and racing bikes when he's not writing about or performing PCB layout. His column is produced by Cadence Design Systems and runs monthly

FIGURE 1. A scheduling tool helps keep the progress front and center.

technology will be a factor of all the above parameters.

It seems flippant in hindsight, but I used to ask how many engineers are on the project. The old saying goes, if you want three opinions, ask two engineers. The various subject matter experts believe their function to be the most important. Getting mixed messages based on different priorities puts us on the throne of King Solomon. There should always be a lead engineer who makes the final decisions. When conflicting instructions come to light, loop in that leader.

**Captive designers:** No plan survives contact ... Most of us are captive designers. The rule here is everything changes except the tape-out date. Some of you may remember the *Peanuts* cartoon strip in which Charlie Brown would attempt to kick the football. Inevitably, his foil Lucy would pull the ball away, leaving poor Charlie Brown on his back. It was a recurring theme: He never once got a foot on the ball.

That's a metaphor for board design if you're expecting to go from start to finish without a course-correction (FIGURE 2). After Google bought Nest, one of the Nest PCB designers wanted to join the Chrome team. I interviewed the guy and recommended approval of his transfer. For one thing, he knew how to code in Pearl and other tools for automating the drudgery.

The program manager asked him for a time estimate for a complex smartphone breakout board. He was savvy enough to quote three months based on the usual co-development with a large team. He was being too real, and the PM wasn't having it. Not knowing his projection when she asked for my opinion, I said two months, best case, but it would not surprise me if it went four.

That was also "too real," so it became one of those team efforts. Even with partitioning and sending the design out to

FIGURE 2. A Gantt chart helps visualize scheduling dependencies.

a service bureau every night, it took just under three months. That included Saturdays and short shifts on Sundays to keep the outside vendors on track. In the end, schematic and outline revisions were out of our control. It's difficult enough when you have not done something before. When a brand-new team does something for the first time, count on half-again more for expected churn.

The most optimistic people in the business seem to go into program management. They may put the PCB designer nominally in charge of driving the schedule, yet we have virtually no authority over the team that ultimately determines the outcome. It is easy to get ahead of yourself when working alone at your desk.

Adding to that uncertainty, some people are unconcerned with the schedule in the first place. Perfection, or simply better, is the enemy of good enough. Digital circuits either work or they don't. It's the analog engineers (I am one) who chase that last bit of performance. Prototypes will always require some improvements, and you won't know what those improvements are until you have that first round of hardware.

#### When it comes to schedule progress, sharing is caring. Simply sharing the data at the end of each day may not be enough. Asking one question related to the work may be sufficient to get the other people to look at the design. You're making design decisions all day long.

A real-life example goes like this: The vias under the SOC are too closely spaced to allow placement of the capacitors. We have to find one mil somewhere. Should we reduce the via size, the pad size or the allowable pad-to-via airgap?

If you make that decision yourself, then you own the problem should one arise. Let's say you take the third choice, reducing the airgap from four mils to three. Then, two days

> after tape-out, the vendor calls and says there is risk of exposed metal because of solder mask expansion. It's a little late to be thinking about the padstack options.

> Getting to the end date with a viable board takes strong communication. The more urgent the schedule, the more you must be risk-averse. Respinning that critical-path layout is a much bigger schedule hit than taking the time to get buy-in on the deviation. No one likes surprises. Take a cue from Charlie Brown to avoid those traps.

# Today's Best Technologies are the Roadmap to an Even Better Future

From autos to airplanes, change is in the air.

2020 HAS BEEN an unusual and challenging year, although many of us can be thankful for the resilience of high-tech industries. Indeed, activity has surged in some sectors, and generally the outlook is relatively buoyant.

In my other role as president of the EIPC (European Institute for the PCB Community), I moderated the Institute's Technical Snapshot webinar last November, at which Dr. Shiuh-Kao Chiang of Prismark described how various sectors have fared. While 5G infrastructure rollouts slowed and handset shipments fell about 10%, the PC market has been buoyed by the increase in work-from-home, and certain consumer markets such as wearables and smart appliances have also done well. Overall, he noted a surprising robustness across the electronics, semiconductor and substrate markets.

The automotive sector has been among the hardest hit, along with conventional commercial aerospace. Rebuilding after the damage to sales caused by the pandemic is just one of the challenges facing vehicle manufacturers right now. They are also contending with the push toward higher levels of driving automation, mandatory smart systems such as autonomous emergency braking, and real-time V2X capabilities, which are expensive to develop. At the same time, governments are signaling their intentions to accelerate electrification, which will require all manufacturers to move their entire product ranges to hybrid-electric or pure battery-EV platforms. The UK government has brought its intended start date forward to 2030. There is no doubt about the urgency, although I am sure at least hybrid-EVs will prove a steppingstone to the kinds of vehicles we use in the future.

Technical progress often happens this way. Consider where we are now with low-energy lighting, for example. Filament bulbs were the dominant technology lighting homes and had changed little in a hundred years. As we saw the imperative to reduce the energy consumed by lighting, we first adopted compact fluorescent lamps (CFLs). Disliked for many reasons, they could be slow to reach full brightness. The lumen output degraded badly over time, and they presented a hazardous waste problem at end of life. Clearly, the world needed to step beyond these and realize a better solution.

Today's solid-state domestic lighting is enabled by innovations in LED fabrication, of course, and by the enhanced thermal performance of insulated metal substrate (IMS) technology, developed within the PCB industry. We are now rewarded with even better lighting, not only more energy-efficient than those early CFLs but with improved reliability and more options than ever to create various lighting effects to suit our moods and activities. Hybrid-EVs and battery-electric vehicles as we know them today have some notable drawbacks. Carrying both internal combustion and electric power systems makes today's hybrids heavier and more expensive than is ideal. Also, problems are associated with sourcing rare materials such as lithium, which is an issue because Li-ion is currently the most suitable battery technology. Natural lithium deposits are dwindling, although mining remains more cost-effective than reclaiming the material from scrap batteries. Nevertheless, automotive electrification has helped create a sizeable market for Li-ion battery recycling that should reach \$17 billion by 2027.

I'm optimistic the coming transition to hybrids and EVs will be just the beginning of our journey toward even better vehicles. They will be enabled by a variety of technologies, some of which are already known, while others remain undiscovered. Prospects are great for PCB stators, for example. These not only save the weight and losses of traditional laminated-iron cores but also allow direct integration of circuitry for important features such as sensing, condition monitoring, and IoT connectivity.

Insofar as energy for EVs is concerned, the hydrogen fuel cell could help relieve demand for lithium. Easy and fast to recharge, it could alleviate range anxiety, while at the same time permitting a significant reduction in battery size. On the other hand, this, too, could be a steppingstone toward another solution that will be more efficient and safer, easier to live with, and ready to offer more rewarding experiences than any we can imagine today.

In addition to road vehicles, shipping and aviation are elements of the transportation mix heavily dependent on combustion engines. The shipping industry is under pressure to move from traditional heavy fuel oil, with or without the use of exhaust scrubbing to remove sulfur-based compounds, in favor of cleaner fossil fuels or, ultimately, electrification. Leading logistics businesses and technology developers are teaming up to create solutions such as high-capacity marine batteries, high-power low-voltage diesel-electric hybrid drives, and hydrogen fuel-cell generators. Ferries, which cover short distances along fixed routes, could be the first step toward full electrification of long-distance shipping.

In the mission to decarbonize aviation, leading aircraft manufacturers are taking their first steps with

continued on pg. 38

ALUN MORGAN is technology ambassador at Ventec International Group (ventec-group. com); alun.morgan@ ventec-europe.com.

### PCEA 2020: Small Rearview Mirror, Big Windshield

A successful first year promises even bigger things to come.

IN THIS MONTH'S forward-driving column, I glance back at PCEA's year in "rearview," which included an energetic jump-start, some challenging air filter retrofitting, some remote diagnostics, and a final refueling at a successful virtual chapter meeting. Next, I hit cruise control and rely on PCEA chairman Stephen Chavez, who focuses on what lies ahead between the vanishing points of highways 2020 and 2021. As always, I'll also point out some interesting events for you to consider attending.

#### PCEA Updates

The past year can be viewed as one of the many good metaphors based on cars and driving, pointing out the differences in size between a rearview mirror and a windshield. You only need to glance in a rearview mirror when backing up or trying to see what may be overtaking you. But if you're driving forward, your main focus should be on the large, clear windshield to see what's coming.

2020 was a great year for the PCEA. It had to be because it's the only one we've had. A group of designers, engineers and PCB industry professionals found themselves looking for a new role after the dissolution of the IPC Designers Council in November 2019. The group was not ready to hang up their passion for highlighting and representing PCB designers. Additionally, they acknowledged a more intimate organizational structure was needed to better cultivate and grow relationships with all vital stakeholders to understand and communicate each other's requirements during the vital phases of design, manufacturing, procurement and test.

In January, meetings were called, and the group

came together to prepare the vision and restart as a

grassroots organization with a mission to collaborate,

educate and inspire the electronics industry to create

better printed circuits. However, the group soon found

themselves masked and quarantined, as did virtu-

ally all the electronics industry. Meeting over the past

months, the PCEA was forged and incorporated as a

nonprofit. Stephen Chavez established this monthly

column a few years ago, prior to the launch of the

PCEA. He delegated it to me after he was named chair-

KELLY DACK, CIT, CID+, is the communication officer for the Printed Circuit Engineering Association (PCEA). Read past columns or contact Dack; kelly. dack.pcea@gmail. com.

In less than a year, the foundation of the PCEA has been laid. The organization held its grand opening event online and counts over 1,000 members among many local chapters itching to meet again. More recently, the San Diego and Phoenix chapters hosted a successful virtual chapter meeting attended by over 50

industry professionals from all over, including Canada.

#### October PCEA Chapter Meeting

Local chapter presidents Luke Hausherr (San Diego chapter) and Randy Kumagai (Phoenix chapter) kicked off the meeting on Oct. 28 with greetings and an introduction to PCEA chairman Stephen Chavez. Steph gave an overview and called on people to spread the word that the PCEA was ready to fulfill its mission of leadership, membership and continually growing industry sponsorship. Recent sponsor Insulectro delivered a technical session on design innovation related to PCB materials, given by VP of technology Chris Hunrath and technical director of design education Mike Creeden, who is also PCEA vice chairman (FIG-URES 1 and 2).

Topics covered included:

- Design innovation

- Hybrid stackup models

- Material properties and considerations

- Effects of loss tangent

- Mixing laminates

- Embedded capacitance

- Advanced HDI structures.

After the presentation, the chapters hosted a raffle with some outstanding prizes. Luke selected the winners (FIGURE 3). The grand prize was a seat of PCB Library Expert, thoughtfully provided by PCB Libraries.

#### Message from the Chairman

by Stephen Chavez, MIT, CID+

What a year! We will never forget 2020. With everything happening in the world today, it amazes me how many have adapted to the virtual world, didn't break stride in meeting today's challenges, and continue to be successful. Our industry's evolution waits for no one, and many have stepped up to the challenge and conquered it. When I think about how 2020 unfolded for the PCEA, we have far exceeded our initial expectations and goals for the year.

From our grand opening on Jul. 14, our membership continues to see strong growth month after month. We are not only growing within the US, but we also have internal growth. Our local and regional PCEA chapters have seen momentum and success. We now have 10 active domestic and international chapters, with eight chapters in their infancy and many others coming soon.

What excites me most about the chapter activities is how each of the chapters is collaborating and

man of the PCEA.

functioning as one collective to better the industry. Even for those of us who have been around for many years and actively involved within the industry, this chapter-to-chapter communication and activity has not been seen before. We truly have collaboration, inspiration and education taking place, especially within our chapters, from one virtual event to another. There is an exciting buzz within the industry about the PCEA.

If these activities aren't enough to make you want to join the collective, then check out our industry affiliations and collaboration, both domestic and international, which is seeing the same type of growth. Our sponsorships also continue to make strides as we continue to get positive feedback and buyin to what the PCEA is all about. And there are a lot of webinars offered for free, so take advantage of them when you can.

Our future looks extremely bright. For 2021, look for more activities, collaboration and synergy among all PCEA chapters. You'll also see growth with our industry affiliates and sponsors to solidify our mission to collaborate, inspire and educate. The year will be even better.

If you have not yet joined the collective, I highly encourage you to do so by visiting our website at pce-a.org and becoming a member.

I continue to wish everyone and their families health and safety. I wish you all much success in 2021.

#### Next Month

As our leader, Steph is doing his job to set the vision, and the PCEA executive staff will be meeting again soon. We will take feedback from the local chapters and work with our sponsors to make concrete plans for PCEA events to help the industry connect and become more educated. I will report on the materialization of these evolving plans in our first column of 2021, so stay tuned.

#### **Upcoming Events**

- Mar. 8-12: IPC Apex Expo (Online)

- Apr. 13-15: DesignCon (San Jose, CA)

- May 10-12: PCB East (Marlborough, MA)

- May 11-13: IPC High-Reliability Forum 2021 (Baltimore, MD)

- Jun. 7-10: Zuken Innovation World (Scottsdale, AZ)

- Aug. 31-Sept. 3: PCB West (Santa Clara, CA)

- Nov. 10: PCB Carolina (Raleigh, NC)

Spread the word. If you have a significant electronics industry event that you would like to announce, please send me the details at kelly.dack.pcea@gmail.com, and we will consider adding it to the list.

#### Conclusion

It's sometimes a relief to look in your rearview mirror and clearly see what you've left behind. But through a dirty windshield, covered with Covid-19 and other challenges, it can be daunting to drive forward without vision. At the PCEA, we want to be the windshield wipers or the sponge and squeegee to help you wipe away your printed circuit engineering apprehensions. Our collective will help you see where your industry is going, inspire you to take the wheel, hit the gas, and enjoy the ride. Now is a great time to check us out at pcea-a.org and make a New Year's resolution to rideshare with us. We're in it for the long haul and have many experienced designated drivers.

See you next month or sooner!

FIGURE 1. Mike Creeden.

FIGURE 2. Chris Hunrath.

FIGURE 3. Luke Hausherr.

### Cutting Your Losses Upfront in PCB Design

A methodology for selecting the right material and the right price point.

WHEN I STARTED writing this column a couple years ago, I wondered how much I'd have to say. An experienced media guy told me to watch my inbox for topics and questions that may be of general interest. That turned out to be excellent advice. Here's one such example.

"What is the best laminate for a loss budget of x dB for y inches? I was thinking in terms of Panasonic Megtron 6 or something like it."

Megtron 6 is an excellent material, but it's not cheap and it's not the only horse in the race. My response was to focus on a loss and material-planning *methodology* rather than making a firm material recommendation.

Why we care. Everything that improves material performance – in particular, reductions in loss – comes at a price. *Loss* versus *cost* is a classic optimization problem. Designers want to pay just enough to meet loss requirements, but not more than they need to.

In the past, speeds were slow, layer counts were low, dielectric constants (aka Dk or Er) and loss tangents (aka dissipation factor, or Df) were high, design margins were wide, copper roughness didn't matter, and glass-weave styles didn't matter. We called dielectrics "FR-4," and their properties didn't matter much.

As speeds increased in the 1990s and after, PCB fabricators acquired software tools for designing stackups and dialing-in target impedances. In the process, they acquired PCB laminate libraries, providing proposed stackups to their OEM customers, typically late in the design process, including material thicknesses, copper thickness, dielectric constant and trace widths often

weeks or months after initial signal-integrity simulation and analysis should have taken place.

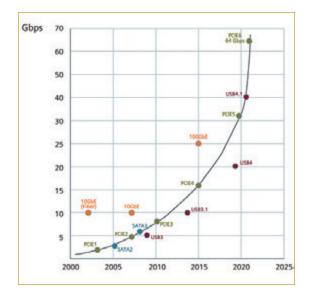

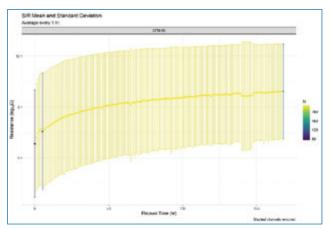

As speeds continued to increase, design margins continued to tighten and OEM engineers began tracking signals in millivolts (mV) and picoseconds (ps). **FIGURE 1** shows these trends starting in 2000. Note in particular the PCI Express trajectory. Critical factors for signal integrity now include not only impedance, but loss, copper roughness and glass-weave skew. Indeed, everything that happens in the process of physically building a PCB affects signal quality in a negative way, and the details need to be accounted for across not just one PCB stackup, but across stackups from every PCB fabricator involved with a design.

5dB interconnect loss at 5GHz. Let's say we're targeting 5dB total interconnect loss at 5GHz for a 15" stripline run length using 0.5 oz. copper. We'll ignore vias for this example and just focus on the laminate. Experience says this may require a material that's indeed in the Meg6 range, but we don't want to spend more money than we have to, so we'll start with a loss

FIGURE 1. Interconnect speed increases in gigabits per second (Gbps) from 2000.

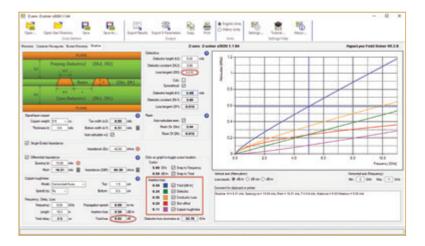

FIGURE 2. Our initial stripline configuration with Df=0.010 and a total loss of 8.82dB. (Image from Z-zero's Z-solver software)

BILL HARGIN has more than 20 years' experience in PCB design software and materials. He is director of everything at Z-zero (z-zero.com); billh@z-zero.com.

tangent (dissipation factor, Df) of 0.010 and see where we're at for a starting point.

**FIGURE 2** shows the result, but some explanation is in order. The blue line represents total loss, which is the sum of all other sources of loss. The orange line is conductor (copper) loss, which is the sum of skin-effect loss (red) and copper roughness (magenta). The graph shows loss in dB per inch, resulting in a total interconnect loss of 8.82dB, a good bit above our target of 5.0dB.

The next place I look is the insertion loss box, which is expanded in **FIGURE 3**. The two biggest contributors to loss here are the skin effect loss and dielectric loss, both at 0.24dB/ in. I know we can cut dielectric loss in half by cutting the Df value in half, so let's give that a try. Changing Df to 0.005 results in a dielectric loss of 0.12dB/in. and a total loss of just over 7.0dB – a significant improvement! Figure 3 also shows loss from copper roughness at 0.11dB/in. is very close to our new dielectric-loss contribution.

Figure 2 shows the core-side roughness for this hypothetical laminate has an Rz roughness of 5.0µm. This corresponds to what many call RTF, or reverse-treated foil. I happen to know that materials in the 0.005 Df range generally offer

smoother copper either by default or as a loss-reduction option. Let's see what would happen with VLP2 or "very-low profile, 2µm" copper. FIGURE 4 shows this change, along with the resulting total interconnect loss, which is now 5.92dB – much closer to our goal.

The total insertion loss is now 0.39dB/in. An easy next step toward achieving our 5dB goal is to create a routing rule that reduces the original 15" to 12". Let's make that change and see where we end up.

*Voila!* Total loss becomes 4.74dB. We now have a Df target for a laminate system, a copper-roughness selection, and a routing rule. That's a lot of progress early in the PCB design process. We can now begin looking for a material that aligns with these parameters.

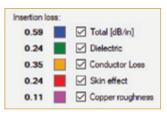

Two good places to initiate that search are with your PCB fabricator(s) or from laminate-vendor data. Several materials that may be worth looking into are shown in **FIGURE 5**, based on their vendor-published Df numbers at 5GHz.

Wrapping up. If you can make material decisions like this early in the design process, you'll avoid prototype surprises down the road or paying more than you need to for laminate systems that are overkill for a design. Making these choices early also allows you to avoid initial laminate lead times that can delay prototypes or early production. Because of prepreg shelf-lives, fabricators carry only the laminates they know they can use within six months or less, following a just-in-time approach. As in many other aspects of life, planning means

more options and fewer surprises. You can feed that expensive signal-integrity solution Dk and Df data from the actual laminate system you're planning to use. Moreover, it may allow you to hold to NPI (new product introduction) schedules more consistently, while at the same time relieving some of the pressure you put on PCB suppliers to make up for poor planning. Everyone wins!

FIGURE 3. The insertion loss box, expanded from Figure 2. The two biggest contributors to loss here are the skin effect loss and dielectric loss, both at 0.24dB/in. (Image from Z-zero's Z-solver software)

FIGURE 4. The trapezoidal shape of innerlayer traces, shown in a stripline cross-section, where w2 is narrower than w1. (Image from Z-zero's Z-solver software)

FIGURE 5. Materials to consider, based on their vendor-published Df numbers at 5GHz. (Image from Z-zero's Z-planner software)

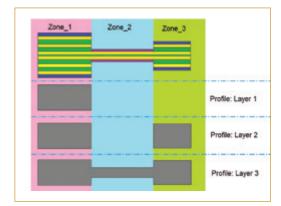

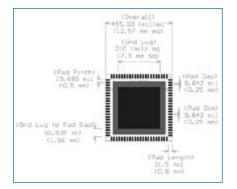

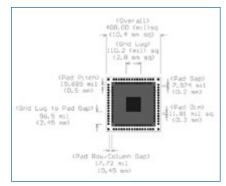

## NEW DFX MODULE for IPC-2581 Slices Design-Manufacturing Time, Errors

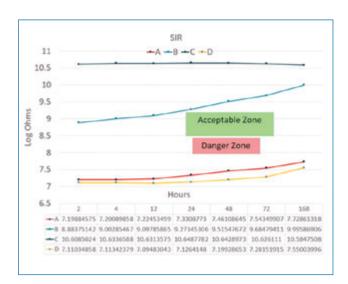

The latest IPC-DPMX standard offers unique bidirectional data exchange between design houses and their manufacturing partners. **by HEMANT SHAH**